www.ti.com | Registers |

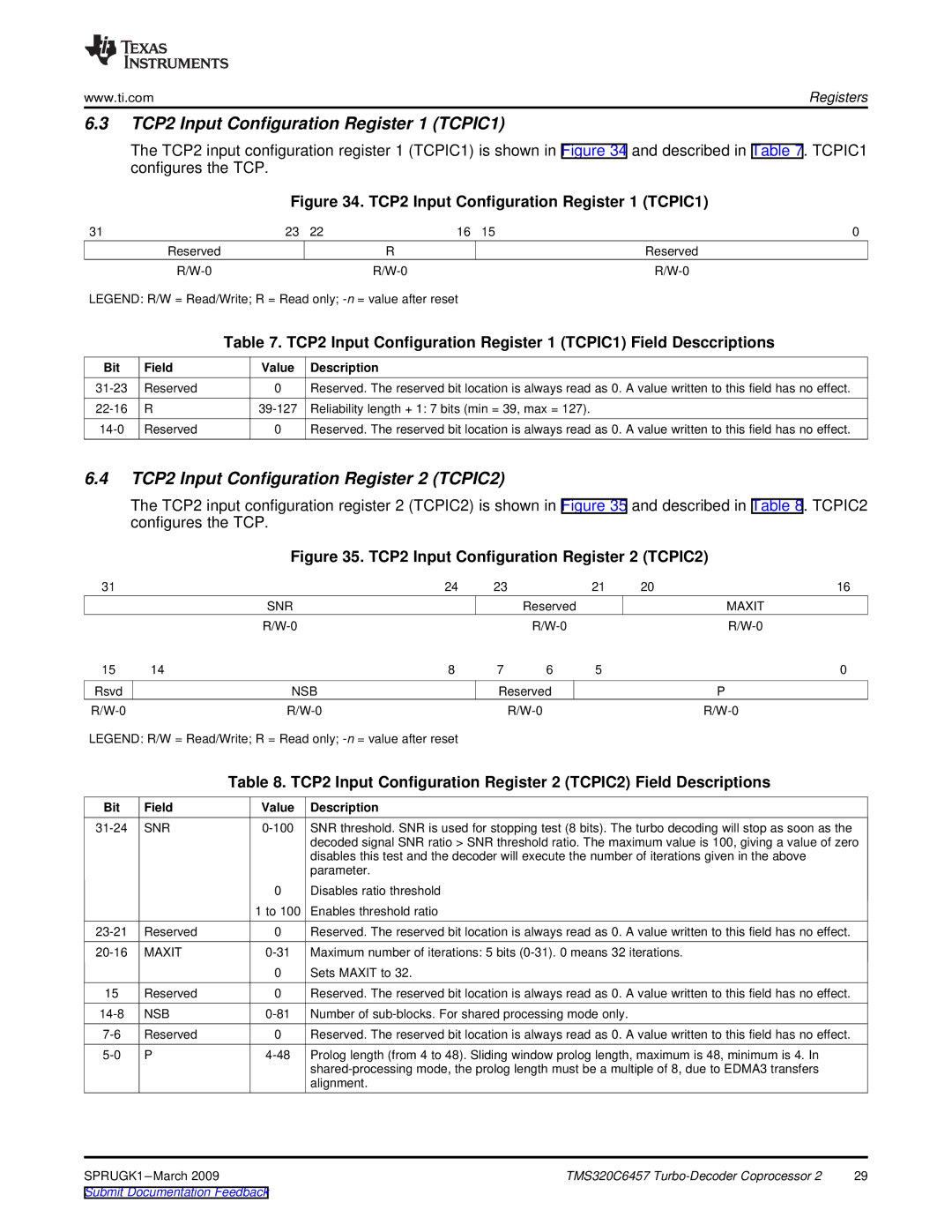

6.3TCP2 Input Configuration Register 1 (TCPIC1)

The TCP2 input configuration register 1 (TCPIC1) is shown in Figure 34 and described in Table 7. TCPIC1 configures the TCP.

Figure 34. TCP2 Input Configuration Register 1 (TCPIC1)

31 | 23 | 22 | 16 | 15 | 0 |

Reserved |

|

| R |

| Reserved |

|

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 7. TCP2 Input Configuration Register 1 (TCPIC1) Field Desccriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. | |

R | Reliability length + 1: 7 bits (min = 39, max = 127). | ||

Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. |

6.4TCP2 Input Configuration Register 2 (TCPIC2)

The TCP2 input configuration register 2 (TCPIC2) is shown in Figure 35 and described in Table 8. TCPIC2 configures the TCP.

Figure 35. TCP2 Input Configuration Register 2 (TCPIC2)

31 |

|

| 24 | 23 |

| 21 | 20 | 16 |

|

| SNR |

|

| Reserved |

|

| MAXIT |

|

|

|

|

|

| |||

15 | 14 |

| 8 | 7 | 6 | 5 |

| 0 |

Rsvd |

| NSB | Reserved |

|

| P | ||

|

|

|

| |||||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

|

| |||

|

| Table 8. TCP2 Input Configuration Register 2 (TCPIC2) Field Descriptions | ||||||

Bit | Field | Value | Description |

|

|

|

|

|

SNR | SNR threshold. SNR is used for stopping test (8 bits). The turbo decoding will stop as soon as the | |||||||

|

|

| decoded signal SNR ratio > SNR threshold ratio. The maximum value is 100, giving a value of zero | |||||

|

|

| disables this test and the decoder will execute the number of iterations given in the above | |||||

|

|

| parameter. |

|

|

|

|

|

|

| 0 | Disables ratio threshold |

|

|

|

|

|

|

| 1 to 100 | Enables threshold ratio |

|

|

|

|

|

Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. | ||||||

MAXIT | Maximum number of iterations: 5 bits |

| ||||||

|

| 0 | Sets MAXIT to 32. |

|

|

|

|

|

15 | Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. | |||||

NSB | Number of |

|

| |||||

Reserved | 0 | Reserved. The reserved bit location is always read as 0. A value written to this field has no effect. | ||||||

P | Prolog length (from 4 to 48). Sliding window prolog length, maximum is 48, minimum is 4. In | |||||||

|

|

| ||||||

|

|

| alignment. |

|

|

|

|

|

TMS320C6457 | 29 | |

Submit Documentation Feedback |

|

|