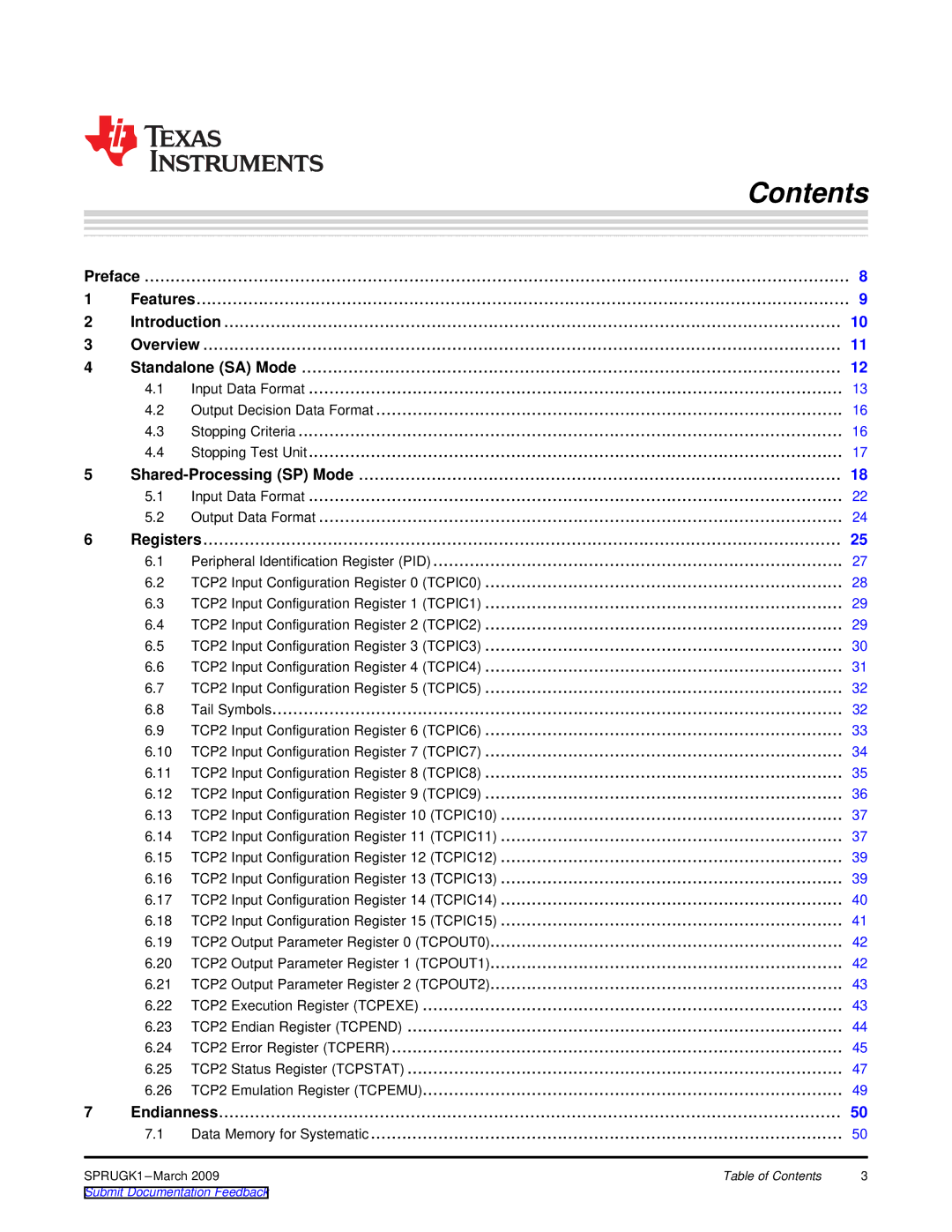

Contents

Preface |

| 8 | ||

1 | Features | 9 | ||

2 | Introduction | 10 | ||

3 | Overview | 11 | ||

4 | Standalone (SA) Mode | 12 | ||

| 4.1 | Input Data Format | 13 | |

| 4.2 | Output Decision Data Format | 16 | |

| 4.3 | Stopping Criteria | 16 | |

| 4.4 | Stopping Test Unit | 17 | |

5 | 18 | |||

| 5.1 | Input Data Format | 22 | |

| 5.2 | Output Data Format | 24 | |

6 | Registers | 25 | ||

| 6.1 | Peripheral Identification Register (PID) | 27 | |

| 6.2 | TCP2 Input Configuration Register 0 (TCPIC0) | 28 | |

| 6.3 | TCP2 Input Configuration Register 1 (TCPIC1) | 29 | |

| 6.4 | TCP2 Input Configuration Register 2 (TCPIC2) | 29 | |

| 6.5 | TCP2 Input Configuration Register 3 (TCPIC3) | 30 | |

| 6.6 | TCP2 Input Configuration Register 4 (TCPIC4) | 31 | |

| 6.7 | TCP2 Input Configuration Register 5 (TCPIC5) | 32 | |

| 6.8 | Tail Symbols | 32 | |

| 6.9 | TCP2 Input Configuration Register 6 (TCPIC6) | 33 | |

| 6.10 | TCP2 Input Configuration Register 7 (TCPIC7) | 34 | |

| 6.11 | TCP2 Input Configuration Register 8 (TCPIC8) | 35 | |

| 6.12 | TCP2 Input Configuration Register 9 (TCPIC9) | 36 | |

| 6.13 | TCP2 Input Configuration Register 10 (TCPIC10) | 37 | |

| 6.14 | TCP2 Input Configuration Register 11 (TCPIC11) | 37 | |

| 6.15 | TCP2 Input Configuration Register 12 (TCPIC12) | 39 | |

| 6.16 | TCP2 Input Configuration Register 13 (TCPIC13) | 39 | |

| 6.17 | TCP2 Input Configuration Register 14 (TCPIC14) | 40 | |

| 6.18 | TCP2 Input Configuration Register 15 (TCPIC15) | 41 | |

| 6.19 | TCP2 Output Parameter Register 0 (TCPOUT0) | 42 | |

| 6.20 | TCP2 Output Parameter Register 1 (TCPOUT1) | 42 | |

| 6.21 | TCP2 Output Parameter Register 2 (TCPOUT2) | 43 | |

| 6.22 | TCP2 Execution Register (TCPEXE) | 43 | |

| 6.23 | TCP2 Endian Register (TCPEND) | 44 | |

| 6.24 | TCP2 Error Register (TCPERR) | 45 | |

| 6.25 | TCP2 Status Register (TCPSTAT) | 47 | |

| 6.26 | TCP2 Emulation Register (TCPEMU) | 49 | |

7 | Endianness | 50 | ||

| 7.1 | Data Memory for Systematic | 50 | |

Table of Contents | 3 | |||