Introduction | www.ti.com |

2Introduction

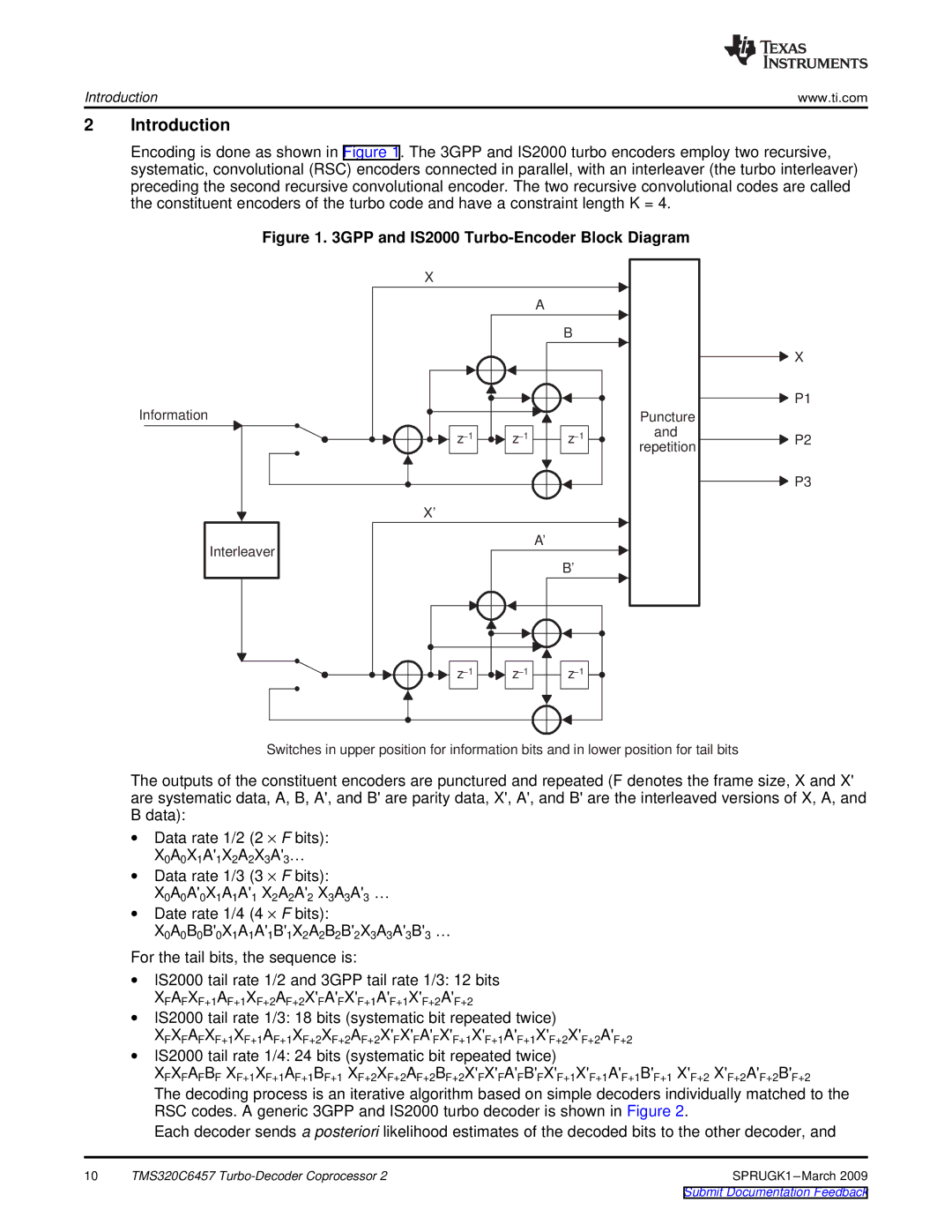

Encoding is done as shown in Figure 1. The 3GPP and IS2000 turbo encoders employ two recursive, systematic, convolutional (RSC) encoders connected in parallel, with an interleaver (the turbo interleaver) preceding the second recursive convolutional encoder. The two recursive convolutional codes are called the constituent encoders of the turbo code and have a constraint length K = 4.

Figure 1. 3GPP and IS2000 Turbo-Encoder Block Diagram

X |

|

|

|

|

| A |

|

|

| B |

|

Information |

|

| Puncture |

z−1 | z−1 | z−1 | and |

|

|

| repetition |

X' |

|

|

|

Interleaver |

| A' |

|

|

|

| |

|

| B' |

|

z−1 | z−1 | z−1 |

|

![]() X

X

![]() P1

P1

![]() P2

P2

![]() P3

P3

Switches in upper position for information bits and in lower position for tail bits

The outputs of the constituent encoders are punctured and repeated (F denotes the frame size, X and X' are systematic data, A, B, A', and B' are parity data, X', A', and B' are the interleaved versions of X, A, and B data):

∙Data rate 1/2 (2 × F bits): X0A0X1A'1X2A2X3A'3…

∙Data rate 1/3 (3 × F bits):

X0A0A'0X1A1A'1 X2A2A'2 X3A3A'3 …

∙Date rate 1/4 (4 × F bits):

X0A0B0B'0X1A1A'1B'1X2A2B2B'2X3A3A'3B'3 …

For the tail bits, the sequence is:

∙IS2000 tail rate 1/2 and 3GPP tail rate 1/3: 12 bits

XFAFXF+1AF+1XF+2AF+2X'FA'FX'F+1A'F+1X'F+2A'F+2

∙IS2000 tail rate 1/3: 18 bits (systematic bit repeated twice)

XFXFAFXF+1XF+1AF+1XF+2XF+2AF+2X'FX'FA'FX'F+1X'F+1A'F+1X'F+2X'F+2A'F+2

∙IS2000 tail rate 1/4: 24 bits (systematic bit repeated twice)

XFXFAFBF XF+1XF+1AF+1BF+1 XF+2XF+2AF+2BF+2X'FX'FA'FB'FX'F+1X'F+1A'F+1B'F+1 X'F+2 X'F+2A'F+2B'F+2

The decoding process is an iterative algorithm based on simple decoders individually matched to the RSC codes. A generic 3GPP and IS2000 turbo decoder is shown in Figure 2.

Each decoder sends a posteriori likelihood estimates of the decoded bits to the other decoder, and

10 | TMS320C6457 |