www.ti.com

Peripheral Architecture

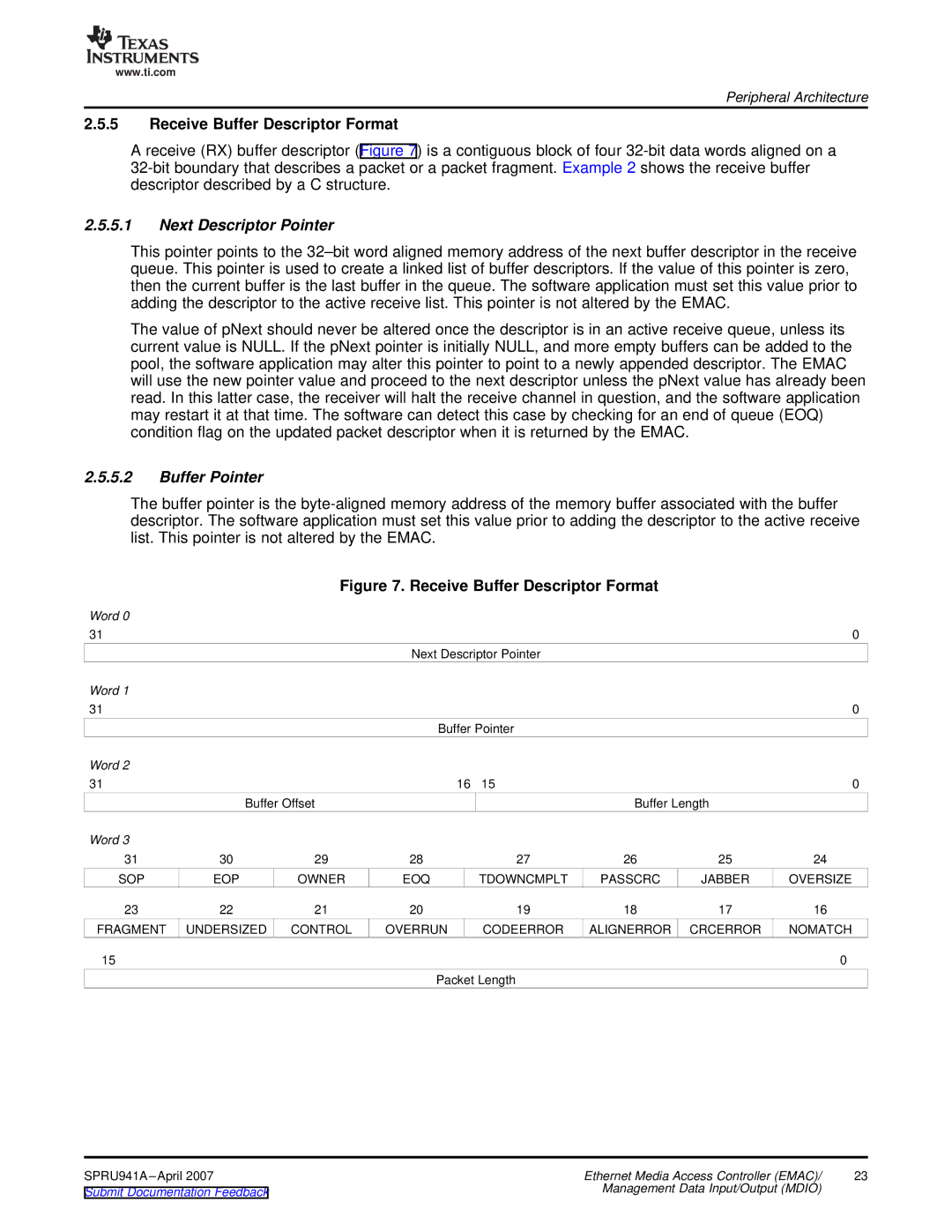

2.5.5Receive Buffer Descriptor Format

A receive (RX) buffer descriptor (Figure 7) is a contiguous block of four

2.5.5.1Next Descriptor Pointer

This pointer points to the

The value of pNext should never be altered once the descriptor is in an active receive queue, unless its current value is NULL. If the pNext pointer is initially NULL, and more empty buffers can be added to the pool, the software application may alter this pointer to point to a newly appended descriptor. The EMAC will use the new pointer value and proceed to the next descriptor unless the pNext value has already been read. In this latter case, the receiver will halt the receive channel in question, and the software application may restart it at that time. The software can detect this case by checking for an end of queue (EOQ) condition flag on the updated packet descriptor when it is returned by the EMAC.

2.5.5.2Buffer Pointer

The buffer pointer is the

|

| Figure 7. Receive Buffer Descriptor Format |

|

| |||

Word 0 |

|

|

|

|

|

|

|

31 |

|

|

|

|

|

| 0 |

|

|

| Next Descriptor Pointer |

|

|

| |

Word 1 |

|

|

|

|

|

|

|

31 |

|

|

|

|

|

| 0 |

|

|

| Buffer Pointer |

|

|

| |

Word 2 |

|

|

|

|

|

|

|

31 |

|

| 16 | 15 |

|

| 0 |

| Buffer Offset |

|

| Buffer Length |

| ||

Word 3 |

|

|

|

|

|

|

|

31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

SOP | EOP | OWNER | EOQ | TDOWNCMPLT | PASSCRC | JABBER | OVERSIZE |

23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

FRAGMENT | UNDERSIZED | CONTROL | OVERRUN | CODEERROR | ALIGNERROR | CRCERROR | NOMATCH |

15 |

|

|

|

|

|

| 0 |

|

|

| Packet Length |

|

|

| |

SPRU941A

Submit Documentation Feedback | Management Data Input/Output (MDIO) |

|