www.ti.com

Ethernet Media Access Controller (EMAC) Registers

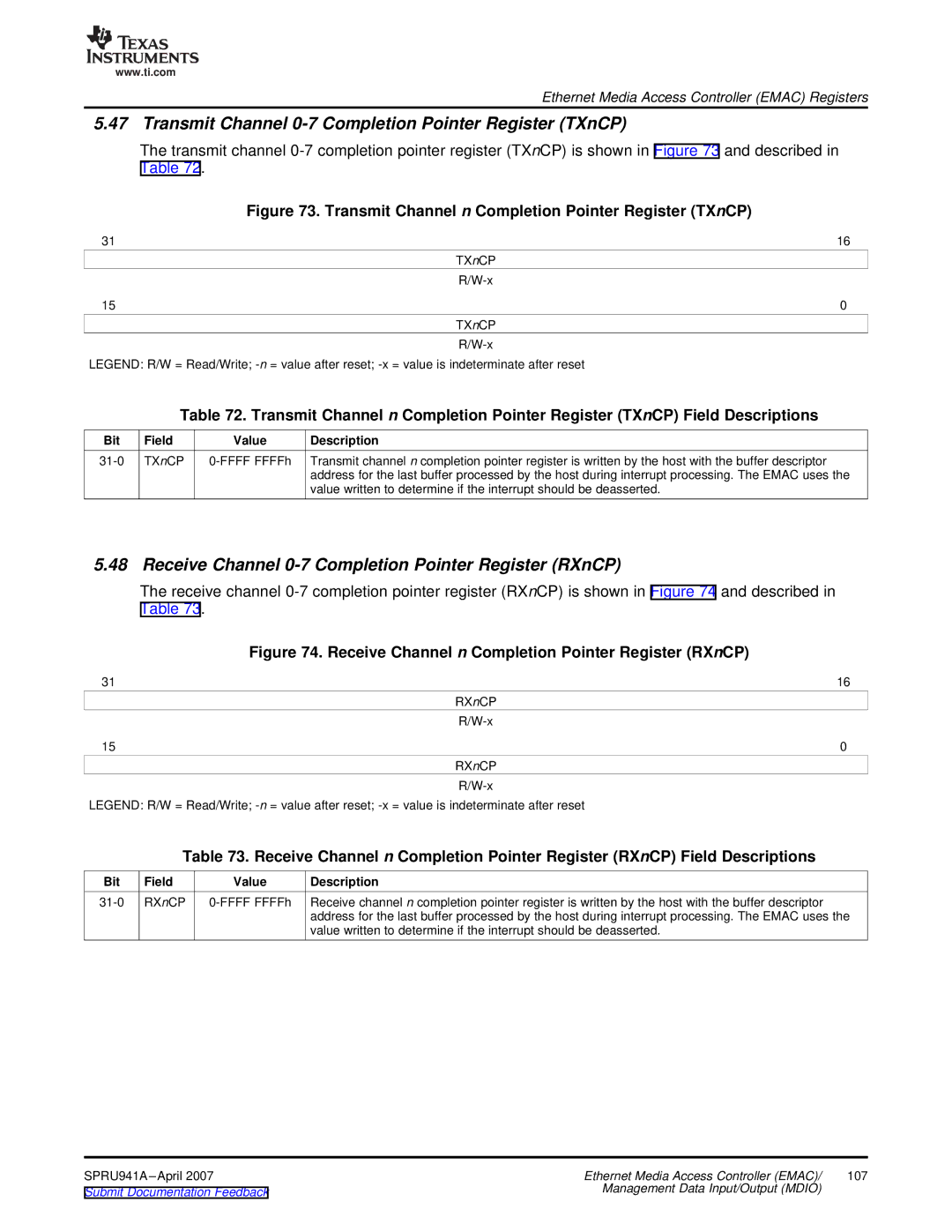

5.47 Transmit Channel 0-7 Completion Pointer Register (TXnCP)

The transmit channel

| Figure 73. Transmit Channel n Completion Pointer Register (TXnCP) |

31 | 16 |

| TXnCP |

| |

15 | 0 |

| TXnCP |

LEGEND: R/W = Read/Write;

Table 72. Transmit Channel n Completion Pointer Register (TXnCP) Field Descriptions

Bit | Field | Value | Description |

TXnCP |

| Transmit channel n completion pointer register is written by the host with the buffer descriptor | |

|

|

| address for the last buffer processed by the host during interrupt processing. The EMAC uses the |

|

|

| value written to determine if the interrupt should be deasserted. |

5.48 Receive Channel 0-7 Completion Pointer Register (RXnCP)

The receive channel

| Figure 74. Receive Channel n Completion Pointer Register (RXnCP) |

31 | 16 |

| RXnCP |

| |

15 | 0 |

| RXnCP |

LEGEND: R/W = Read/Write;

Table 73. Receive Channel n Completion Pointer Register (RXnCP) Field Descriptions

Bit | Field | Value | Description |

RXnCP |

| Receive channel n completion pointer register is written by the host with the buffer descriptor | |

|

|

| address for the last buffer processed by the host during interrupt processing. The EMAC uses the |

|

|

| value written to determine if the interrupt should be deasserted. |

SPRU941A

Submit Documentation Feedback | Management Data Input/Output (MDIO) |

|