www.ti.com

EMAC Control Module Registers

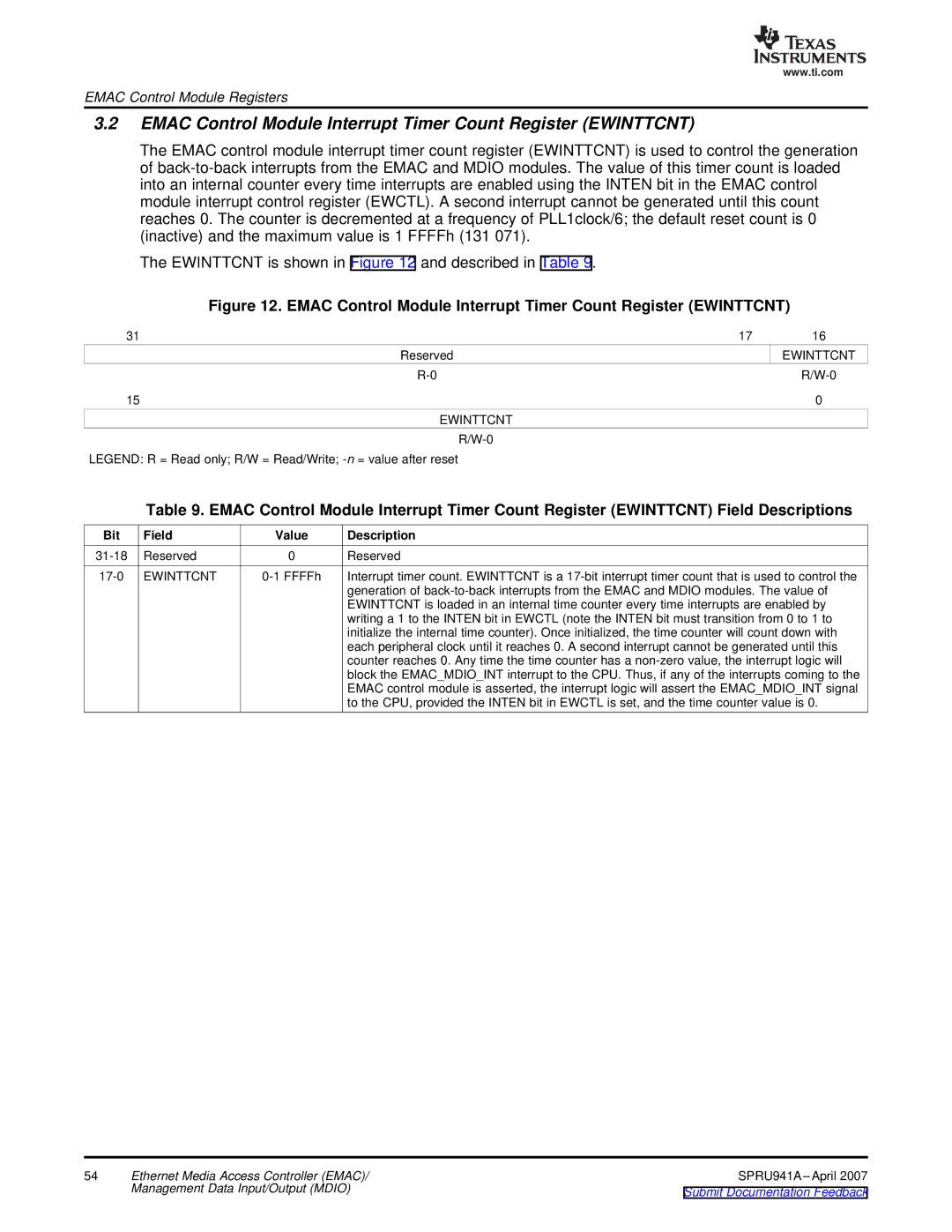

3.2EMAC Control Module Interrupt Timer Count Register (EWINTTCNT)

The EMAC control module interrupt timer count register (EWINTTCNT) is used to control the generation of

The EWINTTCNT is shown in Figure 12 and described in Table 9.

Figure 12. EMAC Control Module Interrupt Timer Count Register (EWINTTCNT)

31 | 17 | 16 |

Reserved |

| EWINTTCNT |

| ||

15 |

| 0 |

EWINTTCNT |

|

|

LEGEND: R = Read only; R/W = Read/Write;

Table 9. EMAC Control Module Interrupt Timer Count Register (EWINTTCNT) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

EWINTTCNT | Interrupt timer count. EWINTTCNT is a | ||

|

|

| generation of |

|

|

| EWINTTCNT is loaded in an internal time counter every time interrupts are enabled by |

|

|

| writing a 1 to the INTEN bit in EWCTL (note the INTEN bit must transition from 0 to 1 to |

|

|

| initialize the internal time counter). Once initialized, the time counter will count down with |

|

|

| each peripheral clock until it reaches 0. A second interrupt cannot be generated until this |

|

|

| counter reaches 0. Any time the time counter has a |

|

|

| block the EMAC_MDIO_INT interrupt to the CPU. Thus, if any of the interrupts coming to the |

|

|

| EMAC control module is asserted, the interrupt logic will assert the EMAC_MDIO_INT signal |

|

|

| to the CPU, provided the INTEN bit in EWCTL is set, and the time counter value is 0. |

54 Ethernet Media Access Controller (EMAC)/SPRU941A

Management Data Input/Output (MDIO) | Submit Documentation Feedback |

|