www.ti.com

Ethernet Media Access Controller (EMAC) Registers

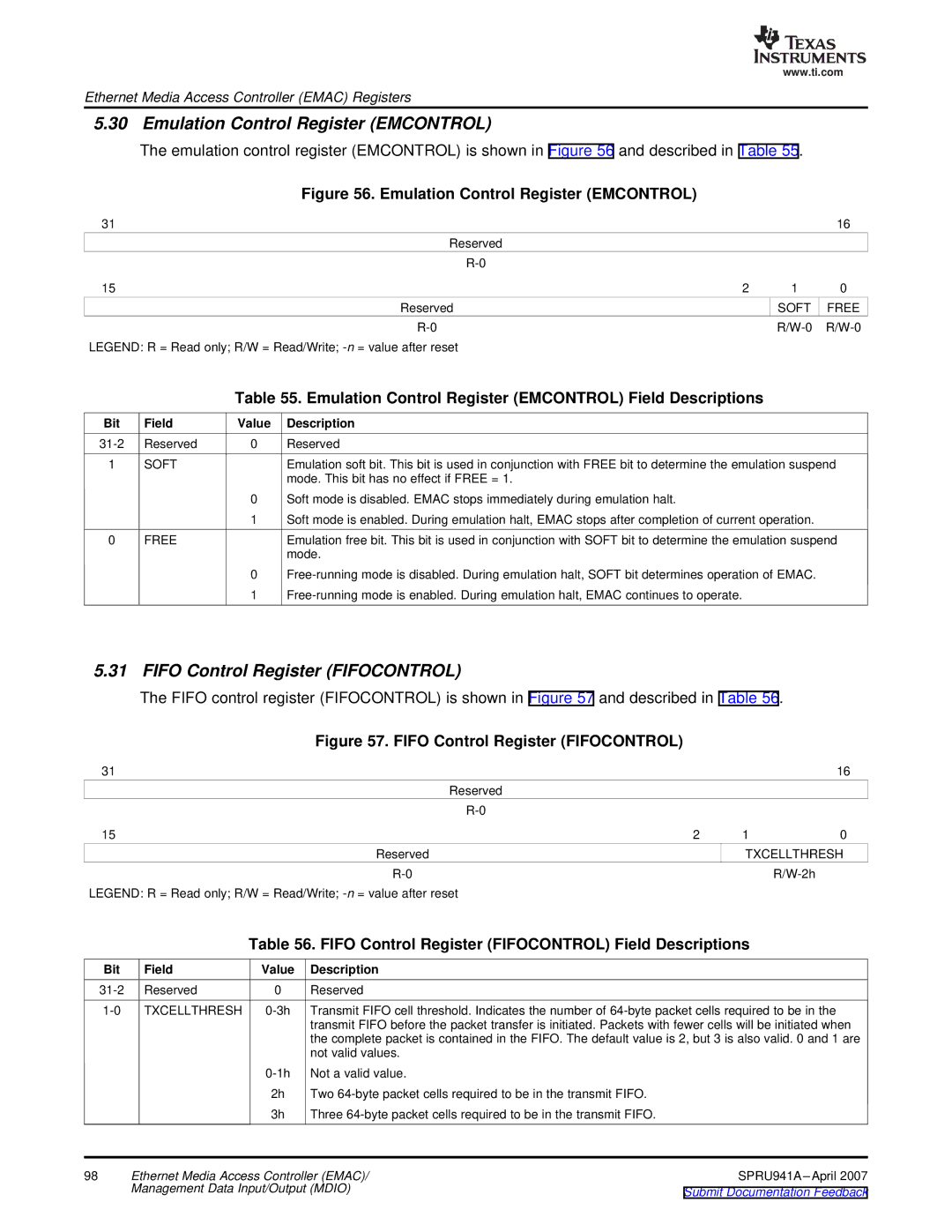

5.30 Emulation Control Register (EMCONTROL)

The emulation control register (EMCONTROL) is shown in Figure 56 and described in Table 55.

Figure 56. Emulation Control Register (EMCONTROL)

31 |

|

| 16 |

Reserved |

|

|

|

|

|

| |

15 | 2 | 1 | 0 |

Reserved |

| SOFT | FREE |

|

LEGEND: R = Read only; R/W = Read/Write;

Table 55. Emulation Control Register (EMCONTROL) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

1 | SOFT |

| Emulation soft bit. This bit is used in conjunction with FREE bit to determine the emulation suspend |

|

|

| mode. This bit has no effect if FREE = 1. |

|

| 0 | Soft mode is disabled. EMAC stops immediately during emulation halt. |

|

| 1 | Soft mode is enabled. During emulation halt, EMAC stops after completion of current operation. |

0 | FREE |

| Emulation free bit. This bit is used in conjunction with SOFT bit to determine the emulation suspend |

|

|

| mode. |

|

| 0 | |

|

| 1 |

5.31 FIFO Control Register (FIFOCONTROL)

The FIFO control register (FIFOCONTROL) is shown in Figure 57 and described in Table 56.

Figure 57. FIFO Control Register (FIFOCONTROL)

31 |

|

| 16 |

| Reserved |

|

|

|

|

| |

15 | 2 | 1 | 0 |

Reserved |

| TXCELLTHRESH | |

|

| ||

LEGEND: R = Read only; R/W = Read/Write;

Table 56. FIFO Control Register (FIFOCONTROL) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

TXCELLTHRESH | Transmit FIFO cell threshold. Indicates the number of | ||

|

|

| transmit FIFO before the packet transfer is initiated. Packets with fewer cells will be initiated when |

|

|

| the complete packet is contained in the FIFO. The default value is 2, but 3 is also valid. 0 and 1 are |

|

|

| not valid values. |

|

| Not a valid value. | |

|

| 2h | Two |

|

| 3h | Three |

98 Ethernet Media Access Controller (EMAC)/SPRU941A

Management Data Input/Output (MDIO) | Submit Documentation Feedback |

|