www.ti.com

Peripheral Architecture

2.8EMAC Module

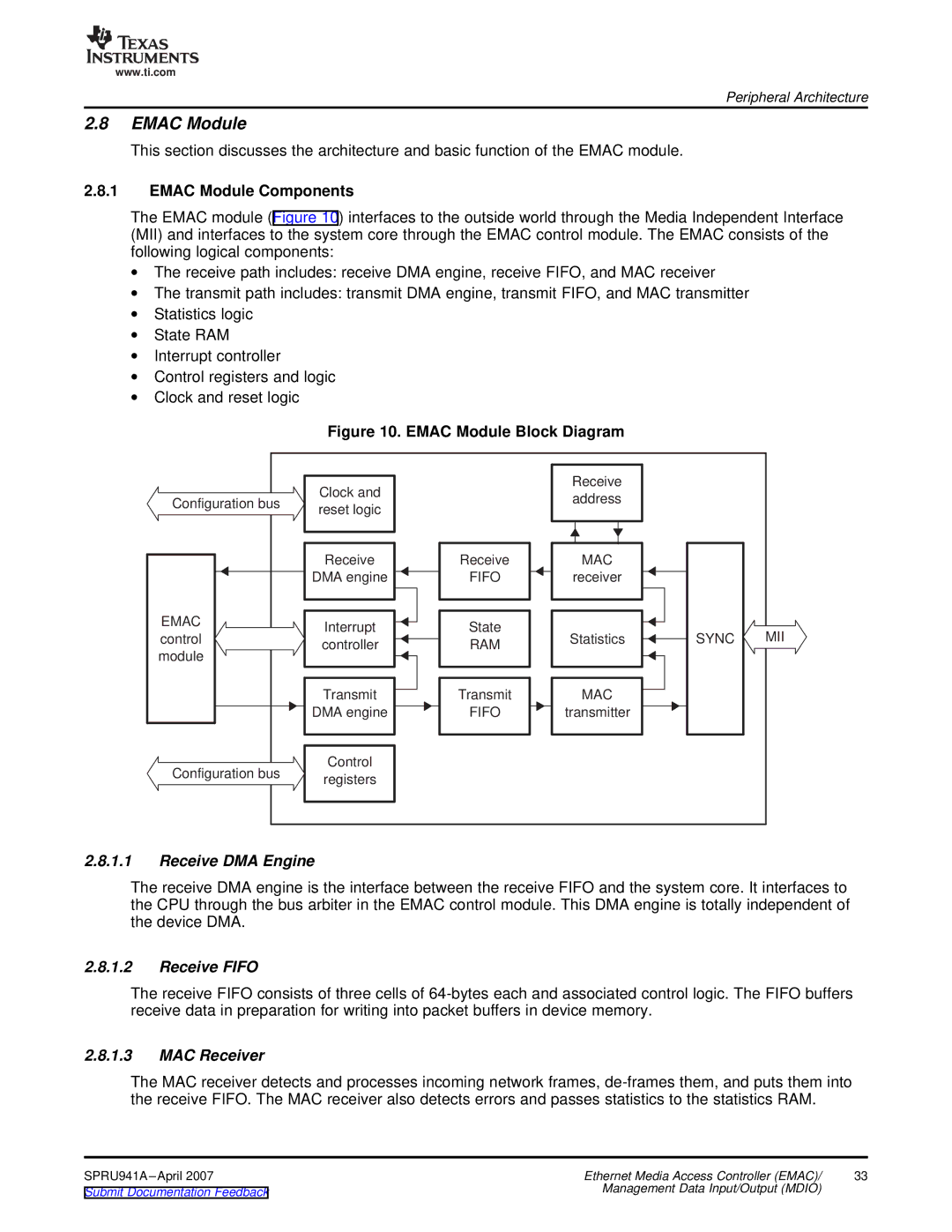

This section discusses the architecture and basic function of the EMAC module.

2.8.1EMAC Module Components

The EMAC module (Figure 10) interfaces to the outside world through the Media Independent Interface (MII) and interfaces to the system core through the EMAC control module. The EMAC consists of the following logical components:

∙The receive path includes: receive DMA engine, receive FIFO, and MAC receiver

∙The transmit path includes: transmit DMA engine, transmit FIFO, and MAC transmitter

∙Statistics logic

∙State RAM

∙Interrupt controller

∙Control registers and logic

∙Clock and reset logic

Figure 10. EMAC Module Block Diagram

| Clock and |

| Receive |

|

| |

Configuration bus |

| address |

|

| ||

reset logic |

|

|

| |||

|

|

|

| |||

|

|

|

|

| ||

| Receive | Receive | MAC |

|

| |

| DMA engine | FIFO | receiver |

|

| |

EMAC | Interrupt | State |

|

| MII | |

control | Statistics | SYNC | ||||

controller | RAM | |||||

module |

|

|

| |||

|

|

|

|

| ||

| Transmit | Transmit | MAC |

|

| |

| DMA engine | FIFO | transmitter |

|

| |

Configuration bus | Control |

|

|

|

| |

registers |

|

|

|

| ||

|

|

|

|

|

2.8.1.1Receive DMA Engine

The receive DMA engine is the interface between the receive FIFO and the system core. It interfaces to the CPU through the bus arbiter in the EMAC control module. This DMA engine is totally independent of the device DMA.

2.8.1.2Receive FIFO

The receive FIFO consists of three cells of

2.8.1.3MAC Receiver

The MAC receiver detects and processes incoming network frames,

SPRU941A

Submit Documentation Feedback | Management Data Input/Output (MDIO) |

|