www.ti.com

Ethernet Media Access Controller (EMAC) Registers

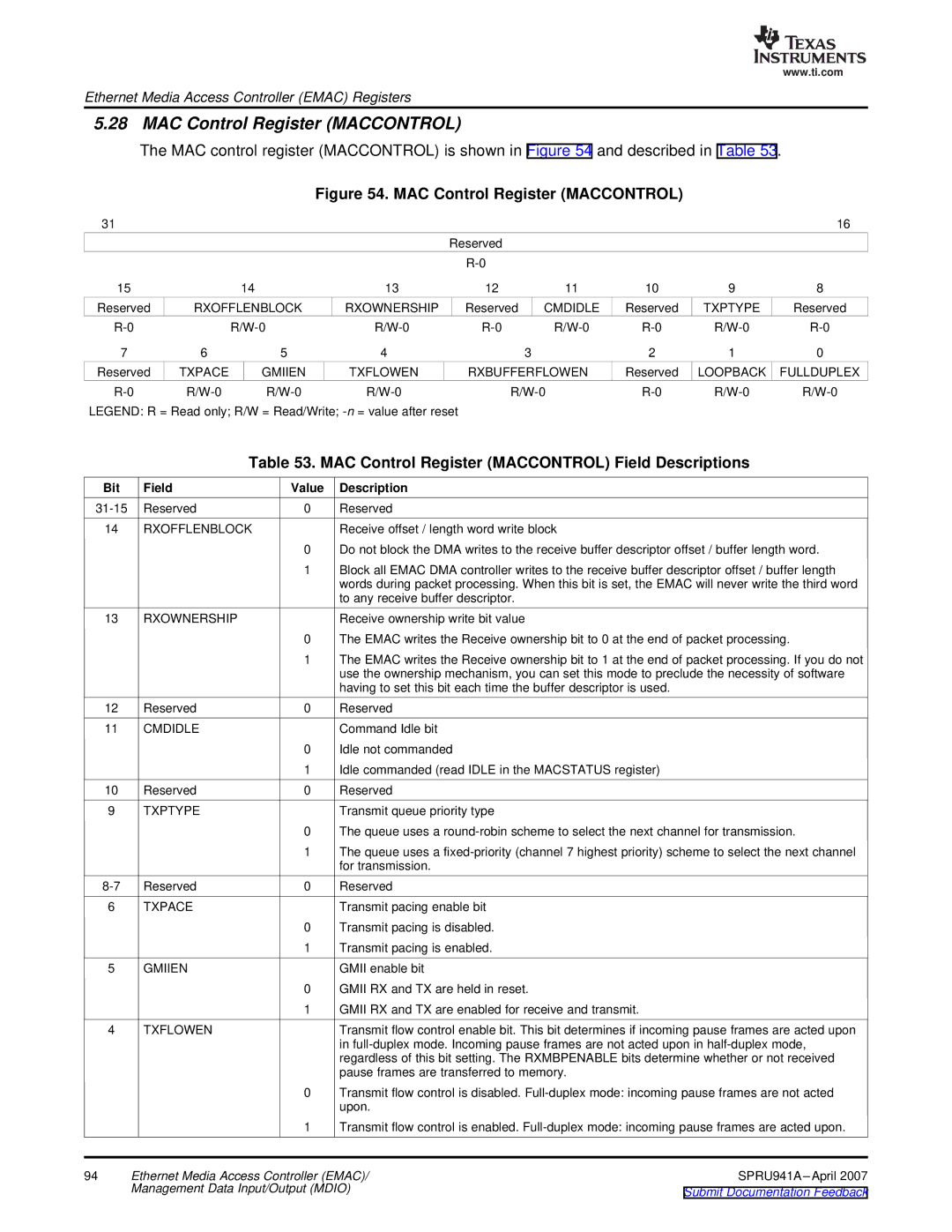

5.28 MAC Control Register (MACCONTROL)

The MAC control register (MACCONTROL) is shown in Figure 54 and described in Table 53.

Figure 54. MAC Control Register (MACCONTROL)

31 |

|

|

|

|

|

|

| 16 |

|

|

|

| Reserved |

|

|

|

|

|

|

|

|

|

|

|

| |

15 |

| 14 | 13 | 12 | 11 | 10 | 9 | 8 |

Reserved | RXOFFLENBLOCK | RXOWNERSHIP | Reserved | CMDIDLE | Reserved | TXPTYPE | Reserved | |

| ||||||||

7 | 6 | 5 | 4 |

| 3 | 2 | 1 | 0 |

Reserved | TXPACE | GMIIEN | TXFLOWEN | RXBUFFERFLOWEN | Reserved | LOOPBACK | FULLDUPLEX | |

LEGEND: R = Read only; R/W = Read/Write;

Table 53. MAC Control Register (MACCONTROL) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

14 | RXOFFLENBLOCK |

| Receive offset / length word write block |

|

| 0 | Do not block the DMA writes to the receive buffer descriptor offset / buffer length word. |

|

| 1 | Block all EMAC DMA controller writes to the receive buffer descriptor offset / buffer length |

|

|

| words during packet processing. When this bit is set, the EMAC will never write the third word |

|

|

| to any receive buffer descriptor. |

13 | RXOWNERSHIP |

| Receive ownership write bit value |

|

| 0 | The EMAC writes the Receive ownership bit to 0 at the end of packet processing. |

|

| 1 | The EMAC writes the Receive ownership bit to 1 at the end of packet processing. If you do not |

|

|

| use the ownership mechanism, you can set this mode to preclude the necessity of software |

|

|

| having to set this bit each time the buffer descriptor is used. |

12 | Reserved | 0 | Reserved |

11 | CMDIDLE |

| Command Idle bit |

|

| 0 | Idle not commanded |

|

| 1 | Idle commanded (read IDLE in the MACSTATUS register) |

10 | Reserved | 0 | Reserved |

9 | TXPTYPE |

| Transmit queue priority type |

|

| 0 | The queue uses a |

|

| 1 | The queue uses a |

|

|

| for transmission. |

Reserved | 0 | Reserved | |

6 | TXPACE |

| Transmit pacing enable bit |

|

| 0 | Transmit pacing is disabled. |

|

| 1 | Transmit pacing is enabled. |

5 | GMIIEN |

| GMII enable bit |

|

| 0 | GMII RX and TX are held in reset. |

|

| 1 | GMII RX and TX are enabled for receive and transmit. |

4 | TXFLOWEN |

| Transmit flow control enable bit. This bit determines if incoming pause frames are acted upon |

|

|

| in |

|

|

| regardless of this bit setting. The RXMBPENABLE bits determine whether or not received |

|

|

| pause frames are transferred to memory. |

|

| 0 | Transmit flow control is disabled. |

|

|

| upon. |

|

| 1 | Transmit flow control is enabled. |

94 Ethernet Media Access Controller (EMAC)/SPRU941A

Management Data Input/Output (MDIO) | Submit Documentation Feedback |

|