www.ti.com

Ethernet Media Access Controller (EMAC) Registers

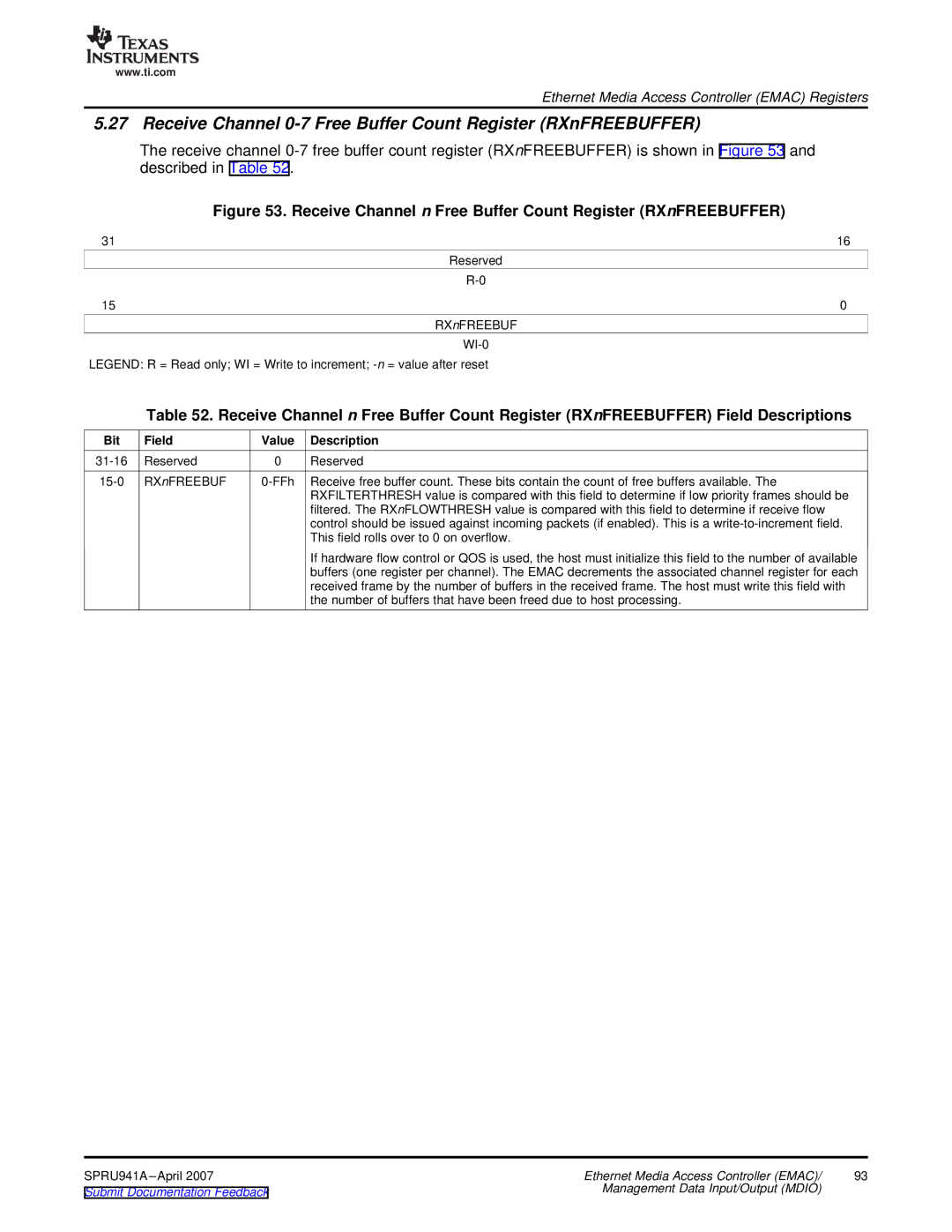

5.27 Receive Channel 0-7 Free Buffer Count Register (RXnFREEBUFFER)

| The receive channel |

| described in Table 52. |

| Figure 53. Receive Channel n Free Buffer Count Register (RXnFREEBUFFER) |

31 | 16 |

| Reserved |

| |

15 | 0 |

| RXnFREEBUF |

LEGEND: R = Read only; WI = Write to increment;

Table 52. Receive Channel n Free Buffer Count Register (RXnFREEBUFFER) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

RXnFREEBUF | Receive free buffer count. These bits contain the count of free buffers available. The | ||

|

|

| RXFILTERTHRESH value is compared with this field to determine if low priority frames should be |

|

|

| filtered. The RXnFLOWTHRESH value is compared with this field to determine if receive flow |

|

|

| control should be issued against incoming packets (if enabled). This is a |

|

|

| This field rolls over to 0 on overflow. |

If hardware flow control or QOS is used, the host must initialize this field to the number of available buffers (one register per channel). The EMAC decrements the associated channel register for each received frame by the number of buffers in the received frame. The host must write this field with the number of buffers that have been freed due to host processing.

SPRU941A

Submit Documentation Feedback | Management Data Input/Output (MDIO) |

|