Introduction

The 31154 has additional hardware support for CompactPCI* Hot Swap and Redundant System Slot via queue flush, arbiter lock, and clock output tristating.

The 31154 supports any combination of

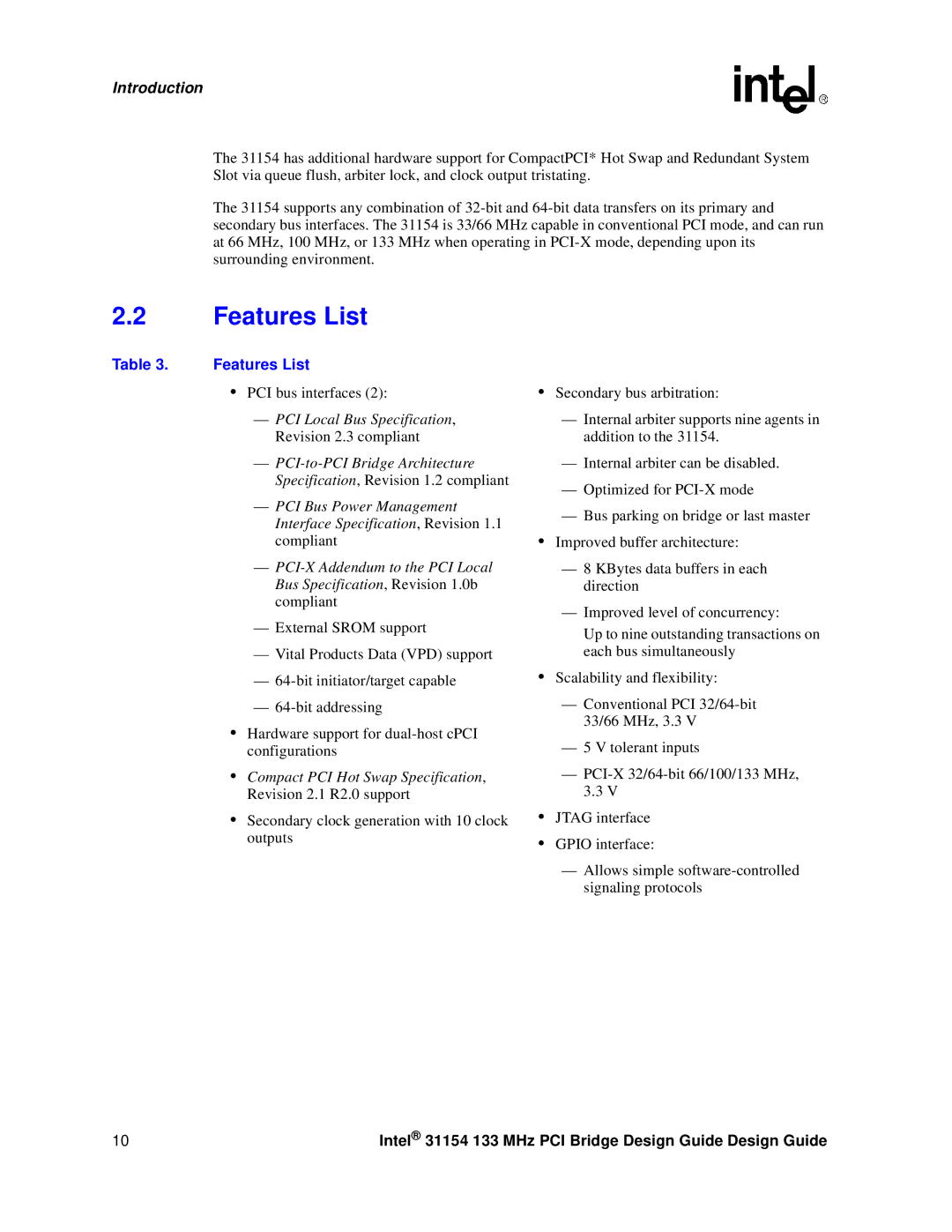

2.2Features List

Table 3. | Features List |

•PCI bus interfaces (2):

—PCI Local Bus Specification, Revision 2.3 compliant

—

—PCI Bus Power Management Interface Specification, Revision 1.1 compliant

—

—External SROM support

—Vital Products Data (VPD) support

—

—

•Hardware support for

•Compact PCI Hot Swap Specification, Revision 2.1 R2.0 support

•Secondary clock generation with 10 clock outputs

•Secondary bus arbitration:

—Internal arbiter supports nine agents in addition to the 31154.

—Internal arbiter can be disabled.

—Optimized for

—Bus parking on bridge or last master

•Improved buffer architecture:

—8 KBytes data buffers in each direction

—Improved level of concurrency:

Up to nine outstanding transactions on each bus simultaneously

•Scalability and flexibility:

—Conventional PCI

—5 V tolerant inputs

—

•JTAG interface

•GPIO interface:

—Allows simple

10 | Intel® 31154 133 MHz PCI Bridge Design Guide Design Guide |