Package Information

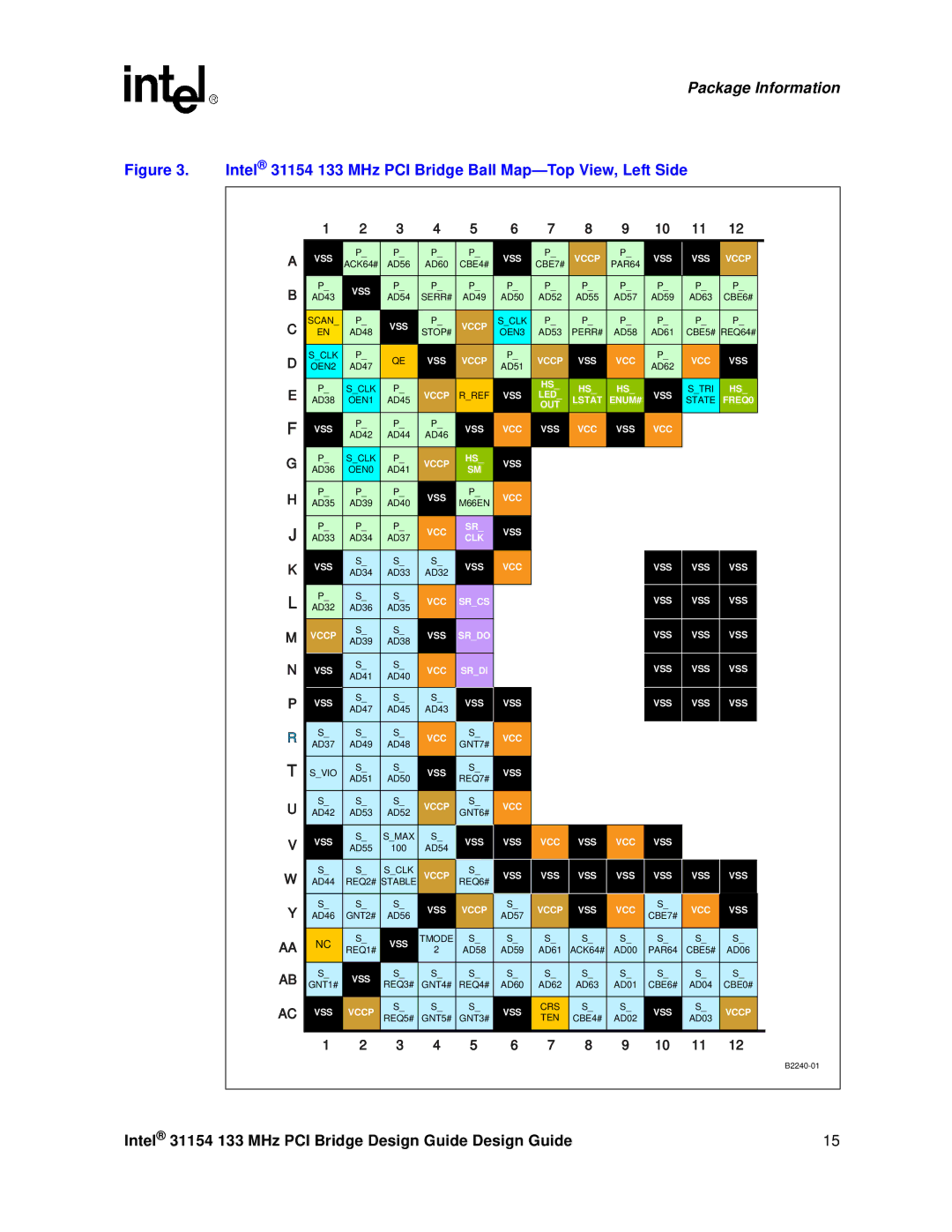

Figure 3. Intel® 31154 133 MHz PCI Bridge Ball Map—Top View, Left Side

|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

|

A | VSS | P_ | P_ | P_ | P_ | VSS | P_ | VCCP | P_ | VSS | VSS | VCCP |

| |

ACK64# | AD56 | AD60 | CBE4# | CBE7# | PAR64 |

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B | P_ | VSS | P_ | P_ | P_ | P_ | P_ | P_ | P_ | P_ | P_ | P_ |

| |

AD43 | AD54 | SERR# | AD49 | AD50 | AD52 | AD55 | AD57 | AD59 | AD63 | CBE6# |

| |||

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C | SCAN_ | P_ | VSS | P_ | VCCP | S_CLK | P_ | P_ | P_ | P_ | P_ | P_ |

| |

EN | AD48 | STOP# | OEN3 | AD53 | PERR# | AD58 | AD61 | CBE5# | REQ64# |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D | S_CLK | P_ | QE | VSS | VCCP | P_ | VCCP | VSS | VCC | P_ | VCC | VSS |

| |

OEN2 | AD47 | AD51 | AD62 |

| ||||||||||

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E | P_ | S_CLK | P_ |

|

|

| HS_ | HS_ | HS_ |

| S_TRI | HS_ |

| |

VCCP | R_REF | VSS | LED_ | VSS |

| |||||||||

AD38 | OEN1 | AD45 | LSTAT | ENUM# | STATE | FREQ0 |

| |||||||

|

|

|

|

|

|

|

| OUT |

|

|

|

|

|

|

F | VSS | P_ | P_ | P_ | VSS | VCC | VSS | VCC | VSS | VCC |

|

|

| |

AD42 | AD44 | AD46 |

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G | P_ | S_CLK | P_ | VCCP | HS_ | VSS |

|

|

|

|

|

|

| |

AD36 | OEN0 | AD41 | SM |

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H | P_ | P_ | P_ | VSS | P_ | VCC |

|

|

|

|

|

|

| |

AD35 | AD39 | AD40 | M66EN |

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J | P_ | P_ | P_ | VCC | SR_ | VSS |

|

|

|

|

|

|

| |

AD33 | AD34 | AD37 | CLK |

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

K | VSS | S_ | S_ | S_ | VSS | VCC |

|

|

| VSS | VSS | VSS |

| |

AD34 | AD33 | AD32 |

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L | P_ | S_ | S_ | VCC | SR_CS |

|

|

|

| VSS | VSS | VSS |

| |

AD32 | AD36 | AD35 |

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M | VCCP | S_ | S_ | VSS | SR_DO |

|

|

|

| VSS | VSS | VSS |

| |

AD39 | AD38 |

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N | VSS | S_ | S_ | VCC | SR_DI |

|

|

|

| VSS | VSS | VSS |

| |

AD41 | AD40 |

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P | VSS | S_ | S_ | S_ | VSS | VSS |

|

|

| VSS | VSS | VSS |

| |

AD47 | AD45 | AD43 |

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R | S_ | S_ | S_ | VCC | S_ | VCC |

|

|

|

|

|

|

| |

AD37 | AD49 | AD48 | GNT7# |

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T | S_VIO | S_ | S_ | VSS | S_ | VSS |

|

|

|

|

|

|

| |

AD51 | AD50 | REQ7# |

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U | S_ | S_ | S_ | VCCP | S_ | VCC |

|

|

|

|

|

|

| |

AD42 | AD53 | AD52 | GNT6# |

|

|

|

|

|

|

| ||||

V | VSS | S_ | S_MAX | S_ | VSS | VSS | VCC | VSS | VCC | VSS |

|

|

AD55 100 | AD54 |

|

| |||||||||

|

|

|

|

|

|

|

|

| ||||

W | S_ | S_ | S_CLK | VCCP | S_ | VSS | VSS | VSS | VSS | VSS | VSS | VSS |

AD44 | REQ2# STABLE | REQ6# | ||||||||||

S_ | S_ | S_ | VSS VCCP | S_ | VCCP VSS | VCC | S_ | VCC | VSS | |

Y AD46 | GNT2# | AD56 | AD57 | CBE7# | ||||||

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

AA | NC | S_ | VSS | TMODE | S_ | S_ | S_ | S_ | S_ | S_ | S_ | S_ | |

REQ1# | 2 | AD58 | AD59 | AD61 | ACK64# | AD00 | PAR64 | CBE5# | AD06 | ||||

AB | S_ | VSS | S_ | S_ | S_ | S_ | S_ | S_ | S_ | S_ | S_ | S_ | |

GNT1# | REQ3# | GNT4# | REQ4# | AD60 | AD62 | AD63 | AD01 | CBE6# | AD04 | CBE0# | |||

|

AC VSS | VCCP | S_ | S_ | S_ | VSS | CRS | S_ | S_ | VSS | S_ | VCCP |

| |

REQ5# | GNT5# | GNT3# | TEN | CBE4# | AD02 | AD03 |

| ||||||

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

|

Intel® 31154 133 MHz PCI Bridge Design Guide Design Guide | 15 |