3.3Functional Outline of Circuit Cards

3.3.1Control Circuit Card

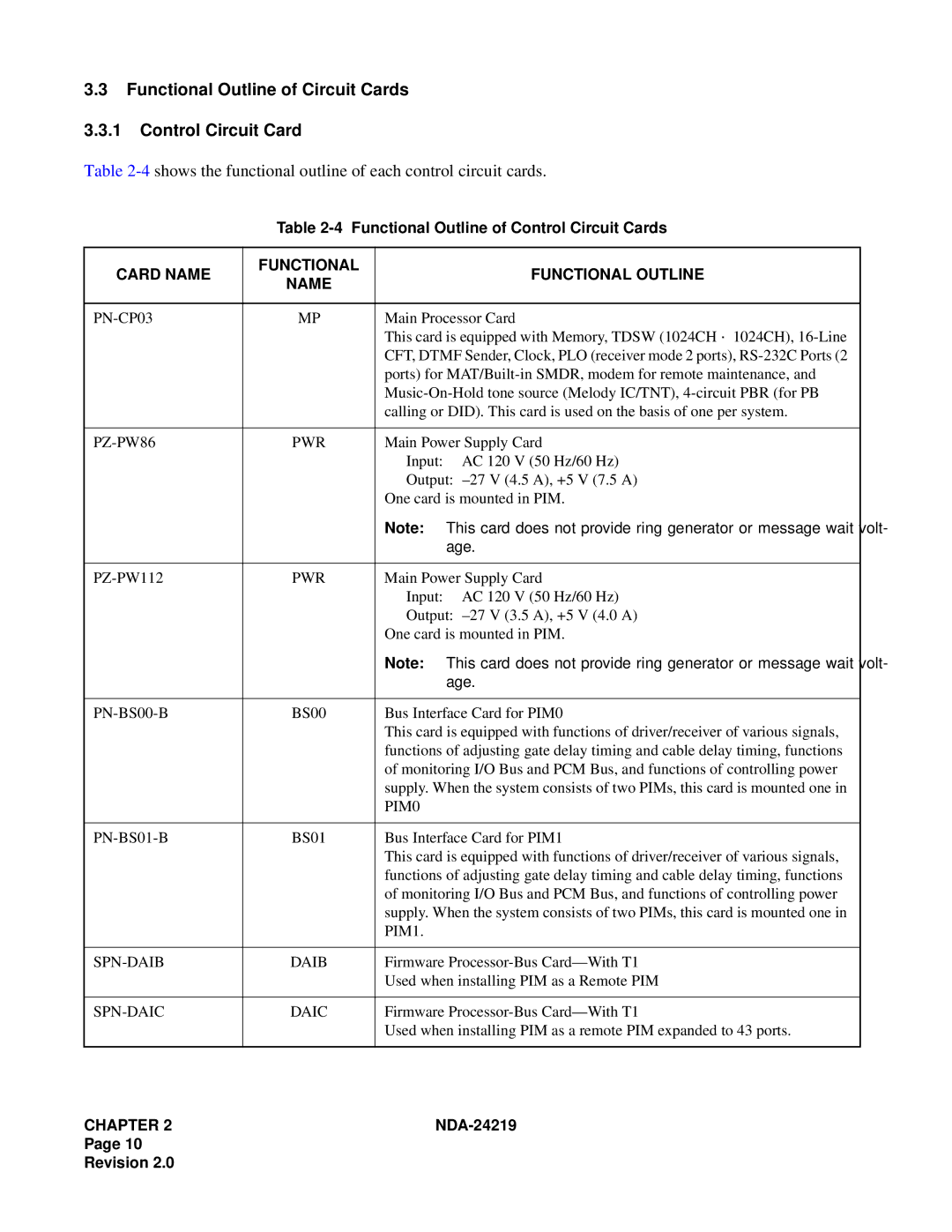

Table 2-4 shows the functional outline of each control circuit cards.

| Table | Functional Outline of Control Circuit Cards | ||

|

|

|

| |

CARD NAME | FUNCTIONAL |

| FUNCTIONAL OUTLINE | |

NAME |

|

| ||

|

|

|

| |

|

|

|

| |

| MP |

| Main Processor Card | |

|

|

| This card is equipped with Memory, TDSW (1024CH × 1024CH), | |

|

|

| CFT, DTMF Sender, Clock, PLO (receiver mode 2 ports), | |

|

|

| ports) for | |

|

|

| ||

|

|

| calling or DID). This card is used on the basis of one per system. | |

|

|

|

| |

| PWR |

| Main Power Supply Card | |

|

|

| Input: | AC 120 V (50 Hz/60 Hz) |

|

|

| Output: | |

|

|

| One card is mounted in PIM. | |

|

|

| Note: | This card does not provide ring generator or message wait volt- |

|

|

|

| age. |

|

|

|

| |

PWR |

| Main Power Supply Card | ||

|

|

| Input: | AC 120 V (50 Hz/60 Hz) |

|

|

| Output: | |

|

|

| One card is mounted in PIM. | |

|

|

| Note: | This card does not provide ring generator or message wait volt- |

|

|

|

| age. |

|

|

|

| |

| BS00 |

| Bus Interface Card for PIM0 | |

|

|

| This card is equipped with functions of driver/receiver of various signals, | |

|

|

| functions of adjusting gate delay timing and cable delay timing, functions | |

|

|

| of monitoring I/O Bus and PCM Bus, and functions of controlling power | |

|

|

| supply. When the system consists of two PIMs, this card is mounted one in | |

|

|

| PIM0 |

|

|

|

|

| |

| BS01 |

| Bus Interface Card for PIM1 | |

|

|

| This card is equipped with functions of driver/receiver of various signals, | |

|

|

| functions of adjusting gate delay timing and cable delay timing, functions | |

|

|

| of monitoring I/O Bus and PCM Bus, and functions of controlling power | |

|

|

| supply. When the system consists of two PIMs, this card is mounted one in | |

|

|

| PIM1. |

|

|

|

|

| |

DAIB |

| Firmware | ||

|

|

| Used when installing PIM as a Remote PIM | |

|

|

|

| |

| DAIC |

| Firmware | |

|

|

| Used when installing PIM as a remote PIM expanded to 43 ports. | |

|

|

|

|

|

CHAPTER 2 |

Page 10

Revision 2.0