Intel® IXP43X Product Line of Network

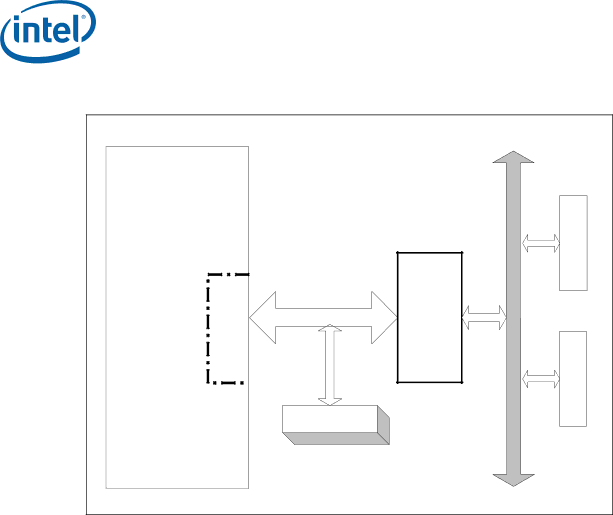

Figure 13. PCI Interface

Intel® IXP43X |

|

|

|

|

|

Product Line of |

|

|

|

|

|

Network Processors |

|

|

|

|

|

|

|

|

| Compact PCI Bus | cPCI J1 |

PCI Interface | PCI Bus | Transparent PCI | Bridge |

| |

| J2 | ||||

|

|

|

|

| cPCI |

| PCI Slots |

|

|

|

|

|

|

|

|

| B 4110- 003 |

3.11.3PCI Option Interface

The IXP43X network processors can be used in a design as a host or as an option device. This section describes how the IXP43X network processors can be connected as an option device to obtain proper functionality. There are slight differences in the hardware interface when designing for option mode. All routing and board recommendations described in this document apply, however the design must use the device pin connections listed in Table 18.

Table 18. PCI Host/Option Interface Pin Description (Sheet 1 of 3)

| Type |

| Option | Description | |

Name |

| Type | |||

Field | |||||

|

| Field |

| ||

|

|

|

| ||

|

|

|

|

| |

PCI_AD[31:0] | I/O | All address/data signals must be | I/O | PCI Address/Data bus | |

connected between the two devices. | |||||

|

|

|

| ||

|

|

|

|

| |

PCI_CBE_N[3:0] | I/O | Connect signals to same pins between | I/O | PCI Command/Byte Enables | |

the two devices. | |||||

|

|

|

| ||

|

|

|

|

| |

PCI_PAR | I/O | Connect signal to same pin between | I/O | PCI Parity | |

the two devices. | |||||

|

|

|

| ||

|

|

|

|

| |

|

| Connect signal to same pin between |

|

| |

PCI_FRAME_N | I/O | the two devices. | I/O | PCI Cycle Frame | |

|

| Connect a |

|

| |

|

|

|

|

| |

|

| Connect signal to same pin between |

|

| |

PCI_TRDY_N | I/O | the two devices. | I/O | PCI Target Ready | |

|

| Connect a |

|

| |

|

|

|

|

| |

Intel® IXP43X Product Line of Network Processors |

|

| |||

HDG |

|

|

| April 2007 | |

48 |

|

|

| Document Number: 316844; Revision: 001US | |