Little Board/P5x Technical Manual

Setup 4 — Chipset Features Setup

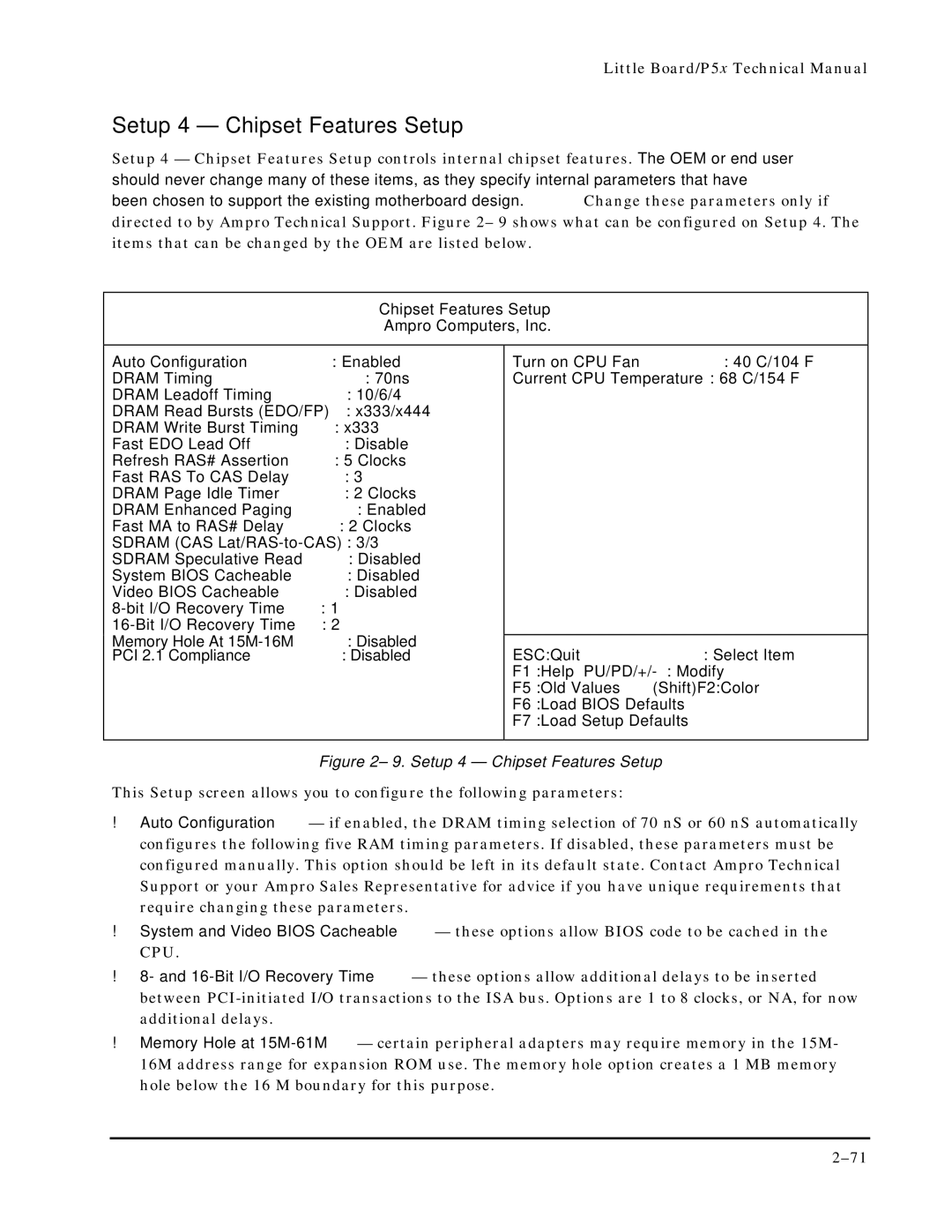

Setup 4 — Chipset Features Setup controls internal chipset features. The OEM or end user should never change many of these items, as they specify internal parameters that have been chosen to support the existing motherboard design. Change these parameters only if directed to by Ampro Technical Support. Figure 2– 9 shows what can be configured on Setup 4. The items that can be changed by the OEM are listed below.

Chipset Features Setup

Ampro Computers, Inc.

Auto Configuration | : Enabled | Turn on CPU Fan |

| : 40°C/104°F | ||

DRAM Timing | : 70ns | Current CPU | Temperature : 68°C/154°F | |||

DRAM Leadoff Timing | : 10/6/4 |

|

|

|

|

|

DRAM Read Bursts (EDO/FP) | : x333/x444 |

|

|

|

|

|

DRAM Write Burst Timing | : x333 |

|

|

|

|

|

Fast EDO Lead Off | : Disable |

|

|

|

|

|

Refresh RAS# Assertion | : 5 Clocks |

|

|

|

|

|

Fast RAS To CAS Delay | : 3 |

|

|

|

|

|

DRAM Page Idle Timer | : 2 Clocks |

|

|

|

|

|

DRAM Enhanced Paging | : Enabled |

|

|

|

|

|

Fast MA to RAS# Delay | : 2 Clocks |

|

|

|

|

|

SDRAM (CAS |

|

|

|

|

| |

SDRAM Speculative Read | : Disabled |

|

|

|

|

|

System BIOS Cacheable | : Disabled |

|

|

|

|

|

Video BIOS Cacheable | : Disabled |

|

|

|

|

|

: 1 |

|

|

|

|

| |

: 2 |

|

|

|

|

| |

Memory Hole At | : Disabled | ESC:Quit | ↑ | ↓ → | ← | : Select Item |

PCI 2.1 Compliance | : Disabled | |||||

|

| F1 :Help | PU/PD/+/- | : Modify | ||

|

| F5 :Old Values | (Shift)F2:Color | |||

|

| F6 :Load BIOS Defaults | ||||

|

| F7 :Load Setup Defaults | ||||

|

|

|

| |||

Figure 2– 9. Setup 4 — Chipset Features Setup |

|

| ||||

This Setup screen allows you to configure the following parameters:

!Auto Configuration — if enabled, the DRAM timing selection of 70 nS or 60 nS automatically configures the following five RAM timing parameters. If disabled, these parameters must be configured manually. This option should be left in its default state. Contact Ampro Technical Support or your Ampro Sales Representative for advice if you have unique requirements that require changing these parameters.

!System and Video BIOS Cacheable — these options allow BIOS code to be cached in the CPU.

!8- and

!Memory Hole at