TTCAN | User’s Manual | Revision 1.6 |

3. Programmer’s Model

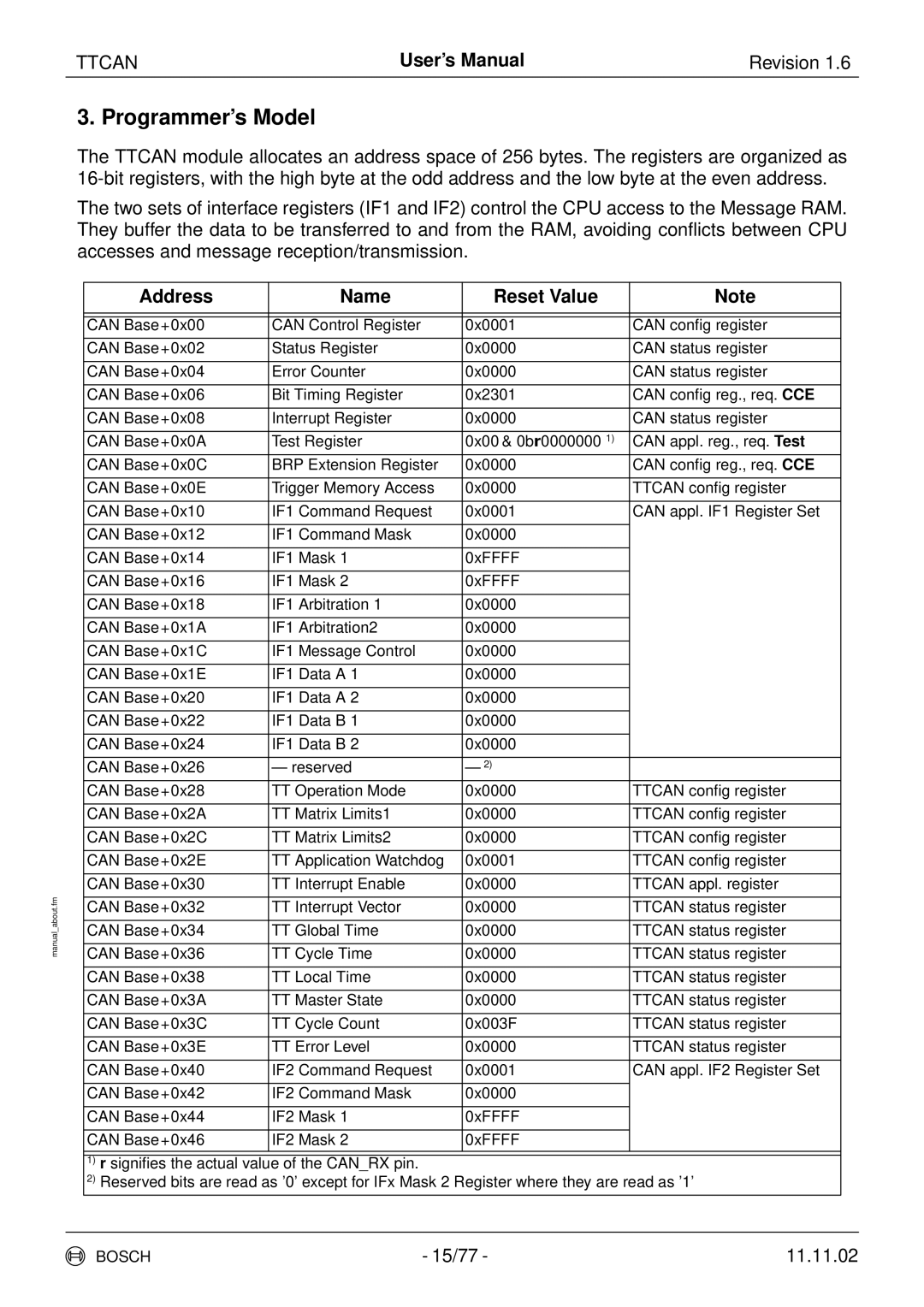

The TTCAN module allocates an address space of 256 bytes. The registers are organized as

The two sets of interface registers (IF1 and IF2) control the CPU access to the Message RAM. They buffer the data to be transferred to and from the RAM, avoiding conflicts between CPU accesses and message reception/transmission.

| Address | Name | Reset Value | Note | |

|

|

|

|

| |

|

|

|

|

| |

| CAN Base+0x00 | CAN Control Register | 0x0001 | CAN config register | |

|

|

|

|

| |

| CAN Base+0x02 | Status Register | 0x0000 | CAN status register | |

|

|

|

|

| |

| CAN Base+0x04 | Error Counter | 0x0000 | CAN status register | |

|

|

|

|

| |

| CAN Base+0x06 | Bit Timing Register | 0x2301 | CAN config reg., req. CCE | |

|

|

|

|

| |

| CAN Base+0x08 | Interrupt Register | 0x0000 | CAN status register | |

|

|

|

|

| |

| CAN Base+0x0A | Test Register | 0x00 & 0br0000000 1) | CAN appl. reg., req. Test | |

| CAN Base+0x0C | BRP Extension Register | 0x0000 | CAN config reg., req. CCE | |

|

|

|

|

| |

| CAN Base+0x0E | Trigger Memory Access | 0x0000 | TTCAN config register | |

|

|

|

|

| |

| CAN Base+0x10 | IF1 Command Request | 0x0001 | CAN appl. IF1 Register Set | |

|

|

|

|

| |

| CAN Base+0x12 | IF1 Command Mask | 0x0000 |

| |

|

|

|

|

| |

| CAN Base+0x14 | IF1 Mask 1 | 0xFFFF |

| |

|

|

|

|

| |

| CAN Base+0x16 | IF1 Mask 2 | 0xFFFF |

| |

|

|

|

|

| |

| CAN Base+0x18 | IF1 Arbitration 1 | 0x0000 |

| |

|

|

|

|

| |

| CAN Base+0x1A | IF1 Arbitration2 | 0x0000 |

| |

|

|

|

|

| |

| CAN Base+0x1C | IF1 Message Control | 0x0000 |

| |

|

|

|

|

| |

| CAN Base+0x1E | IF1 Data A 1 | 0x0000 |

| |

|

|

|

|

| |

| CAN Base+0x20 | IF1 Data A 2 | 0x0000 |

| |

|

|

|

|

| |

| CAN Base+0x22 | IF1 Data B 1 | 0x0000 |

| |

|

|

|

|

| |

| CAN Base+0x24 | IF1 Data B 2 | 0x0000 |

| |

|

|

|

|

| |

| CAN Base+0x26 | — reserved | — 2) |

| |

| CAN Base+0x28 | TT Operation Mode | 0x0000 | TTCAN config register | |

|

|

|

|

| |

| CAN Base+0x2A | TT Matrix Limits1 | 0x0000 | TTCAN config register | |

|

|

|

|

| |

| CAN Base+0x2C | TT Matrix Limits2 | 0x0000 | TTCAN config register | |

|

|

|

|

| |

| CAN Base+0x2E | TT Application Watchdog | 0x0001 | TTCAN config register | |

|

|

|

|

| |

| CAN Base+0x30 | TT Interrupt Enable | 0x0000 | TTCAN appl. register | |

about.fm |

|

|

|

| |

CAN Base+0x32 | TT Interrupt Vector | 0x0000 | TTCAN status register | ||

| |||||

|

|

|

|

| |

manual | CAN Base+0x34 | TT Global Time | 0x0000 | TTCAN status register | |

|

|

|

| ||

CAN Base+0x36 | TT Cycle Time | 0x0000 | TTCAN status register | ||

| |||||

|

|

|

|

| |

| CAN Base+0x38 | TT Local Time | 0x0000 | TTCAN status register | |

|

|

|

|

| |

| CAN Base+0x3A | TT Master State | 0x0000 | TTCAN status register | |

|

|

|

|

| |

| CAN Base+0x3C | TT Cycle Count | 0x003F | TTCAN status register | |

|

|

|

|

| |

| CAN Base+0x3E | TT Error Level | 0x0000 | TTCAN status register | |

|

|

|

|

| |

| CAN Base+0x40 | IF2 Command Request | 0x0001 | CAN appl. IF2 Register Set | |

|

|

|

|

| |

| CAN Base+0x42 | IF2 Command Mask | 0x0000 |

| |

|

|

|

|

| |

| CAN Base+0x44 | IF2 Mask 1 | 0xFFFF |

| |

|

|

|

|

| |

| CAN Base+0x46 | IF2 Mask 2 | 0xFFFF |

| |

|

|

|

|

| |

|

|

|

| ||

| 1) r signifies the actual value of the CAN_RX pin. |

|

| ||

| 2) Reserved bits are read as ’0’ except for IFx Mask 2 Register where they are read as ’1’ | ||||

BOSCH | - 15/77 - | 11.11.02 |