TTCAN | User’s Manual | Revision 1.6 |

4.2.1.4 Oscillator Tolerance Range

The oscillator tolerance range was increased when the CAN protocol was developed from version 1.1 to version 1.2 (version 1.0 was never implemented in silicon). The option to synchronise on edges from dominant to recessive became obsolete, only edges from recessive to dominant are considered for synchronisation. The only CAN controllers to implement protocol version 1.1 have been Intel 82526 and Philips 82C200, both are superseded by successor products. The protocol update to version 2.0 (A and B) had no influence on the oscillator tolerance.

The tolerance range df for an oscillator’s frequency fosc around the nominal frequency fnom

with (1

be met):

I: | df ≤ | |

|

| 2 • (13 • bit_time |

II: | df ≤ | SJW |

It has to be considered that SJW may not be larger than the smaller of the Phase Buffer Segments and that the Propagation Time Segment limits that part of the bit time that may be used for the Phase Buffer Segments.

The combination Prop_Seg = 1 and Phase_Seg1 = Phase_Seg2 = SJW = 4 allows the largest possible oscillator tolerance of 1.58%. This combination with a Propagation Time Segment of only 10% of the bit time is not suitable for short bit times; it can be used for bit rates of up to 125 kBit/s (bit time = 8 ∝s) with a bus length of 40 m.

4.2.1.5 Configuration of the CAN Protocol Controller

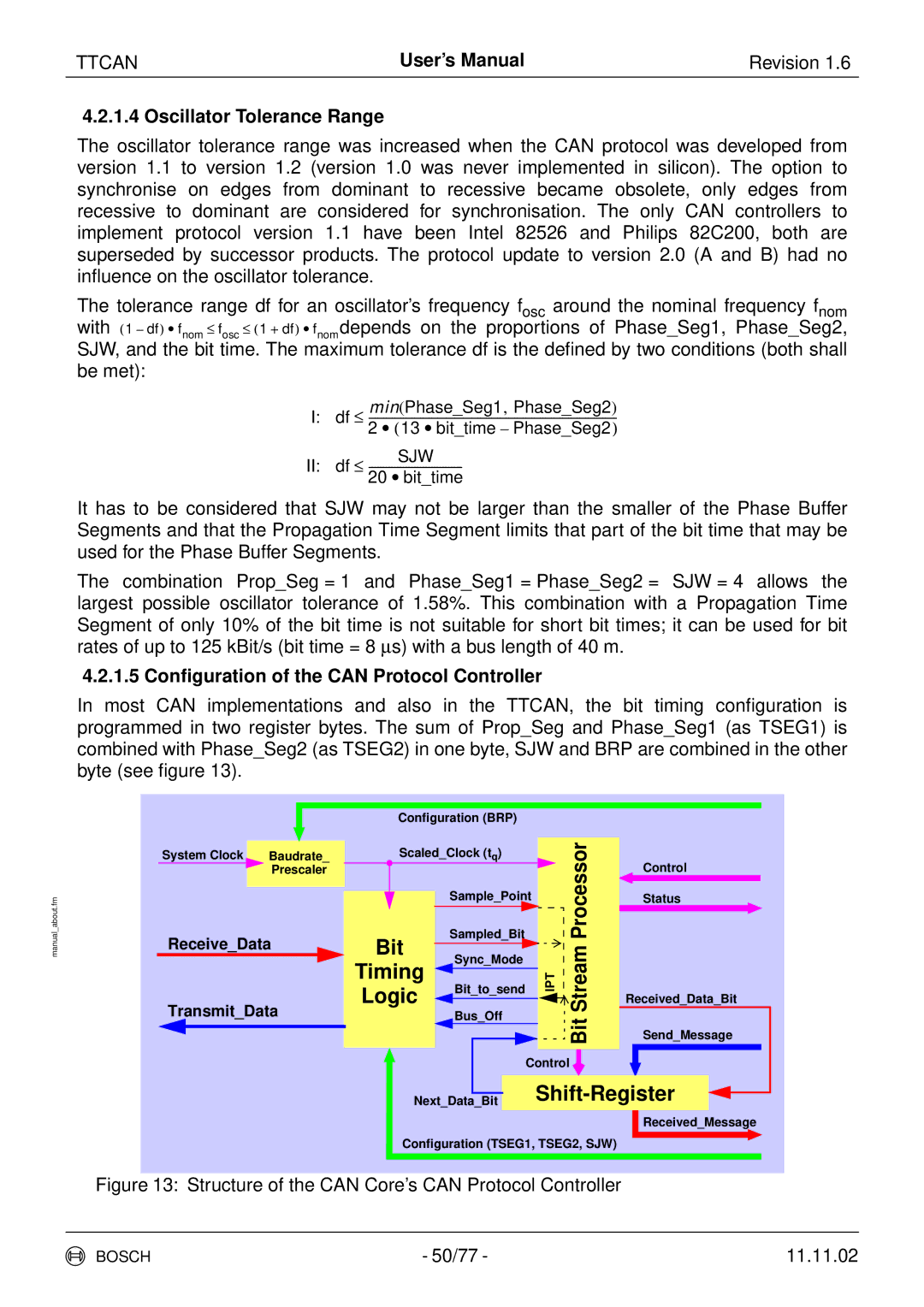

In most CAN implementations and also in the TTCAN, the bit timing configuration is programmed in two register bytes. The sum of Prop_Seg and Phase_Seg1 (as TSEG1) is combined with Phase_Seg2 (as TSEG2) in one byte, SJW and BRP are combined in the other byte (see figure 13).

manual_about.fm

|

| Configuration (BRP) |

|

|

| |

System Clock | Baudrate_ | Scaled_Clock (tq) |

| Processor | Control | |

| Prescaler |

|

|

| ||

|

|

| Sample_Point |

| Status | |

Receive_Data | Bit | Sampled_Bit |

|

| ||

Sync_Mode |

| Stream |

| |||

|

| Timing |

|

| ||

|

| Bit_to_send | IPT |

| ||

|

| Logic | Received_Data_Bit | |||

Transmit_Data |

| |||||

| Bus_Off |

| ||||

|

| Bit |

| |||

|

|

|

|

| Send_Message | |

|

|

|

|

|

| |

|

|

| Control |

|

| |

|

| Next_Data_Bit |

| |||

|

|

|

|

|

| Received_Message |

|

| Configuration (TSEG1, TSEG2, SJW) |

| |||

Figure 13: Structure of the CAN Core’s CAN Protocol Controller

BOSCH | - 50/77 - | 11.11.02 |