TTCAN | User’s Manual | Revision 1.6 | |||

3.4.2 Transmission Request Registers |

|

| |||

|

|

|

|

|

|

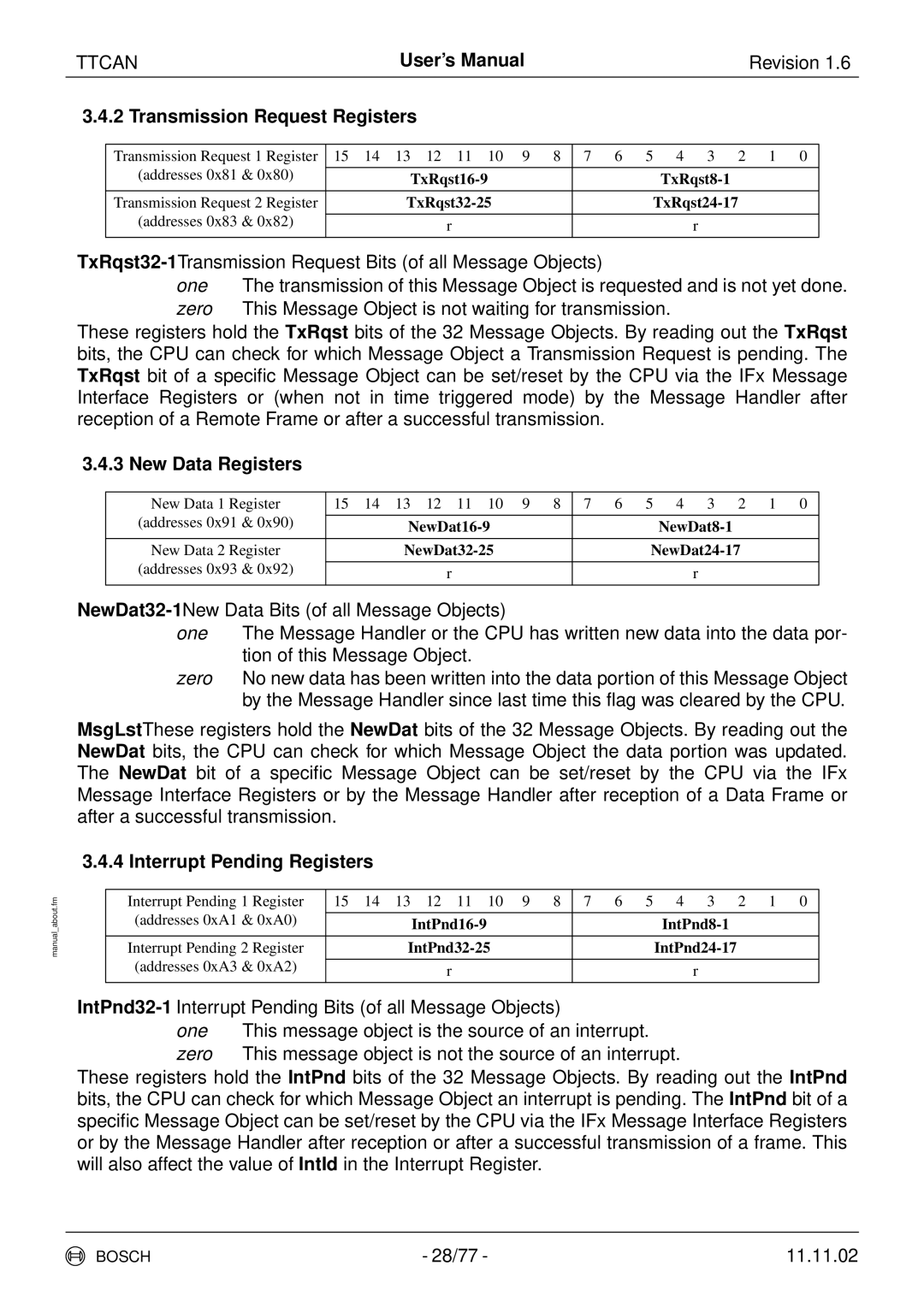

| Transmission Request 1 Register | 15 14 13 12 11 10 9 8 | 7 | 6 5 4 3 2 1 0 |

|

| (addresses 0x81 & 0x80) |

|

|

|

|

|

|

| |||

|

|

|

|

|

|

| Transmission Request 2 Register |

|

| ||

| (addresses 0x83 & 0x82) |

|

|

|

|

| r |

| r |

| |

|

|

|

| ||

|

|

|

|

|

|

one The transmission of this Message Object is requested and is not yet done. zero This Message Object is not waiting for transmission.

These registers hold the TxRqst bits of the 32 Message Objects. By reading out the TxRqst bits, the CPU can check for which Message Object a Transmission Request is pending. The TxRqst bit of a specific Message Object can be set/reset by the CPU via the IFx Message Interface Registers or (when not in time triggered mode) by the Message Handler after reception of a Remote Frame or after a successful transmission.

3.4.3 New Data Registers

New Data 1 Register | 15 14 13 12 11 10 9 8 | 7 | 6 5 4 3 2 1 0 |

(addresses 0x91 & 0x90) |

|

|

|

| |||

|

|

|

|

New Data 2 Register |

| ||

(addresses 0x93 & 0x92) |

|

|

|

r |

| r | |

|

| ||

|

|

|

|

one The Message Handler or the CPU has written new data into the data por- tion of this Message Object.

zero No new data has been written into the data portion of this Message Object by the Message Handler since last time this flag was cleared by the CPU.

MsgLstThese registers hold the NewDat bits of the 32 Message Objects. By reading out the NewDat bits, the CPU can check for which Message Object the data portion was updated. The NewDat bit of a specific Message Object can be set/reset by the CPU via the IFx Message Interface Registers or by the Message Handler after reception of a Data Frame or after a successful transmission.

3.4.4 Interrupt Pending Registers

manual_about.fm

Interrupt Pending 1 Register | 15 14 13 12 11 10 9 8 | 7 | 6 5 4 3 2 1 0 |

(addresses 0xA1 & 0xA0) |

|

|

|

| |||

|

|

|

|

Interrupt Pending 2 Register |

| ||

(addresses 0xA3 & 0xA2) |

|

|

|

r |

| r | |

|

| ||

|

|

|

|

one This message object is the source of an interrupt. zero This message object is not the source of an interrupt.

These registers hold the IntPnd bits of the 32 Message Objects. By reading out the IntPnd bits, the CPU can check for which Message Object an interrupt is pending. The IntPnd bit of a specific Message Object can be set/reset by the CPU via the IFx Message Interface Registers or by the Message Handler after reception or after a successful transmission of a frame. This will also affect the value of IntId in the Interrupt Register.

BOSCH | - 28/77 - | 11.11.02 |