TTCAN | User’s Manual | Revision 1.6 |

manual_about.fm

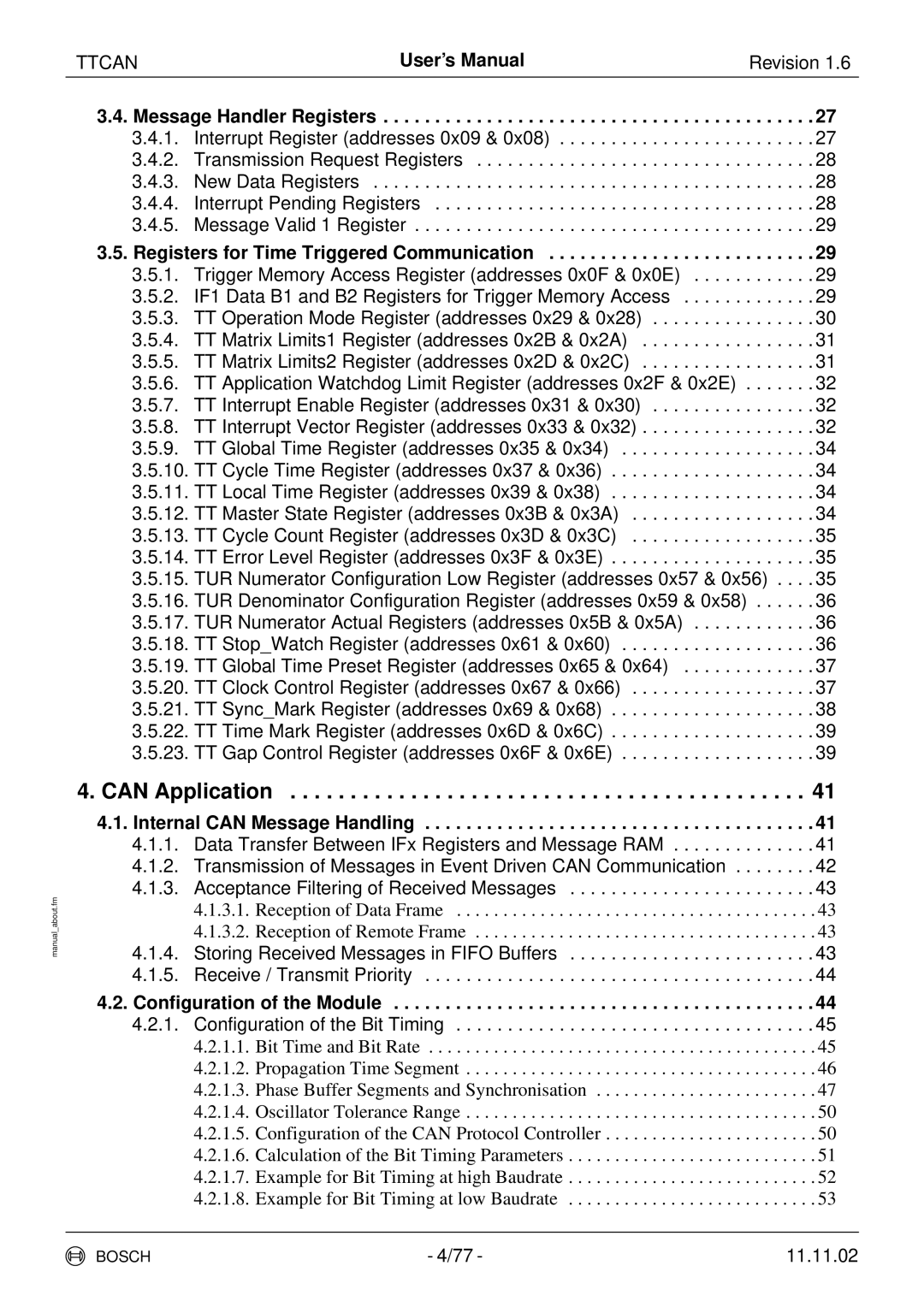

3.4. Message Handler Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 3.4.1. Interrupt Register (addresses 0x09 & 0x08) . . . . . . . . . . . . . . . . . . . . . . . . . 27 3.4.2. Transmission Request Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 3.4.3. New Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 3.4.4. Interrupt Pending Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 3.4.5. Message Valid 1 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.5. Registers for Time Triggered Communication | . 29 |

3.5.1. Trigger Memory Access Register (addresses 0x0F & 0x0E) | . 29 |

3.5.2. IF1 Data B1 and B2 Registers for Trigger Memory Access | . 29 |

3.5.3. TT Operation Mode Register (addresses 0x29 & 0x28) | . 30 |

3.5.4. TT Matrix Limits1 Register (addresses 0x2B & 0x2A) | . 31 |

3.5.5. TT Matrix Limits2 Register (addresses 0x2D & 0x2C) | . 31 |

3.5.6. TT Application Watchdog Limit Register (addresses 0x2F & 0x2E) | . 32 |

3.5.7. TT Interrupt Enable Register (addresses 0x31 & 0x30) | . 32 |

3.5.8. TT Interrupt Vector Register (addresses 0x33 & 0x32) | . 32 |

3.5.9. TT Global Time Register (addresses 0x35 & 0x34) | . 34 |

3.5.10. TT Cycle Time Register (addresses 0x37 & 0x36) | . 34 |

3.5.11. TT Local Time Register (addresses 0x39 & 0x38) | . 34 |

3.5.12. TT Master State Register (addresses 0x3B & 0x3A) | . 34 |

3.5.13. TT Cycle Count Register (addresses 0x3D & 0x3C) | . 35 |

3.5.14. TT Error Level Register (addresses 0x3F & 0x3E) | . 35 |

3.5.15. TUR Numerator Configuration Low Register (addresses 0x57 & 0x56) . . . . 35 | |

3.5.16. TUR Denominator Configuration Register (addresses 0x59 & 0x58) | . 36 |

3.5.17. TUR Numerator Actual Registers (addresses 0x5B & 0x5A) | . 36 |

3.5.18. TT Stop_Watch Register (addresses 0x61 & 0x60) | . 36 |

3.5.19. TT Global Time Preset Register (addresses 0x65 & 0x64) | . 37 |

3.5.20. TT Clock Control Register (addresses 0x67 & 0x66) | . 37 |

3.5.21. TT Sync_Mark Register (addresses 0x69 & 0x68) | . 38 |

3.5.22. TT Time Mark Register (addresses 0x6D & 0x6C) | . 39 |

3.5.23. TT Gap Control Register (addresses 0x6F & 0x6E) | . 39 |

4. CAN Application | 41 |

4.1. Internal CAN Message Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 4.1.1. Data Transfer Between IFx Registers and Message RAM . . . . . . . . . . . . . . 41 4.1.2. Transmission of Messages in Event Driven CAN Communication . . . . . . . . 42 4.1.3. Acceptance Filtering of Received Messages . . . . . . . . . . . . . . . . . . . . . . . . 43

| 4.1.3.1. Reception of Data Frame | 43 |

| 4.1.3.2. Reception of Remote Frame | 43 |

4.1.4. | Storing Received Messages in FIFO Buffers | 43 |

4.1.5. | Receive / Transmit Priority | 44 |

4.2. Configuration of the Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 4.2.1. Configuration of the Bit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 4.2.1.1. Bit Time and Bit Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 4.2.1.2. Propagation Time Segment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 4.2.1.3. Phase Buffer Segments and Synchronisation . . . . . . . . . . . . . . . . . . . . . . . . 47 4.2.1.4. Oscillator Tolerance Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 4.2.1.5. Configuration of the CAN Protocol Controller . . . . . . . . . . . . . . . . . . . . . . . 50 4.2.1.6. Calculation of the Bit Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . 51 4.2.1.7. Example for Bit Timing at high Baudrate . . . . . . . . . . . . . . . . . . . . . . . . . . . 52 4.2.1.8. Example for Bit Timing at low Baudrate . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

BOSCH | - 4/77 - | 11.11.02 |