TTCAN | User’s Manual | Revision 1.6 |

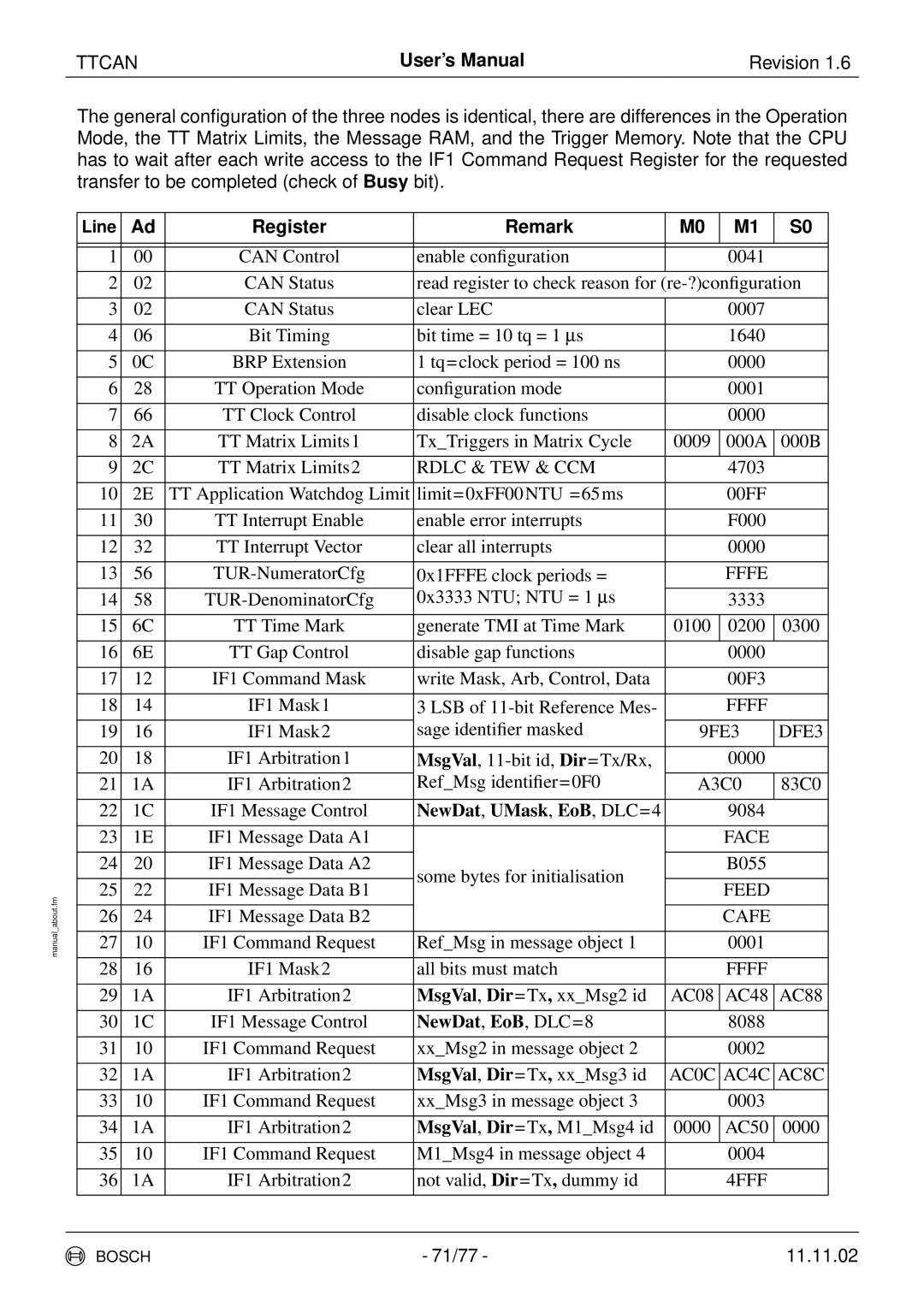

The general configuration of the three nodes is identical, there are differences in the Operation Mode, the TT Matrix Limits, the Message RAM, and the Trigger Memory. Note that the CPU has to wait after each write access to the IF1 Command Request Register for the requested transfer to be completed (check of Busy bit).

| Line | Ad | Register | Remark | M0 | M1 | S0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 | 00 | CAN Control | enable configuration |

| 0041 |

|

|

|

|

|

|

|

|

|

| 2 | 02 | CAN Status | read register to check reason for | |||

|

|

|

|

|

|

|

|

| 3 | 02 | CAN Status | clear LEC |

| 0007 |

|

|

|

|

|

|

|

|

|

| 4 | 06 | Bit Timing | bit time = 10 tq = 1 ∝s |

| 1640 |

|

|

|

|

|

|

|

|

|

| 5 | 0C | BRP Extension | 1 tq=clock period = 100 ns |

| 0000 |

|

|

|

|

|

|

|

|

|

| 6 | 28 | TT Operation Mode | configuration mode |

| 0001 |

|

|

|

|

|

|

|

|

|

| 7 | 66 | TT Clock Control | disable clock functions |

| 0000 |

|

|

|

|

|

|

|

|

|

| 8 | 2A | TT Matrix Limits1 | Tx_Triggers in Matrix Cycle | 0009 | 000A | 000B |

|

|

|

|

|

|

|

|

| 9 | 2C | TT Matrix Limits2 | RDLC & TEW & CCM |

| 4703 |

|

|

|

|

|

|

|

|

|

| 10 | 2E | TT Application Watchdog Limit | limit=0xFF00NTU =65ms |

| 00FF |

|

|

|

|

|

|

|

|

|

| 11 | 30 | TT Interrupt Enable | enable error interrupts |

| F000 |

|

|

|

|

|

|

|

|

|

| 12 | 32 | TT Interrupt Vector | clear all interrupts |

| 0000 |

|

|

|

|

|

|

|

|

|

| 13 | 56 | 0x1FFFE clock periods = |

| FFFE |

| |

|

|

|

| 0x3333 NTU; NTU = 1 ∝s |

|

|

|

| 14 | 58 |

| 3333 |

| ||

|

|

|

|

|

|

|

|

| 15 | 6C | TT Time Mark | generate TMI at Time Mark | 0100 | 0200 | 0300 |

|

|

|

|

|

|

|

|

| 16 | 6E | TT Gap Control | disable gap functions |

| 0000 |

|

|

|

|

|

|

|

|

|

| 17 | 12 | IF1 Command Mask | write Mask, Arb, Control, Data |

| 00F3 |

|

|

|

|

|

|

|

|

|

| 18 | 14 | IF1 Mask1 | 3 LSB of |

| FFFF |

|

|

|

|

| sage identifier masked |

|

| |

| 19 | 16 | IF1 Mask2 | 9FE3 | DFE3 | ||

|

|

|

|

|

|

|

|

| 20 | 18 | IF1 Arbitration1 | MsgVal, |

| 0000 |

|

|

|

|

| Ref_Msg identifier=0F0 |

|

| |

| 21 | 1A | IF1 Arbitration2 | A3C0 | 83C0 | ||

|

|

|

|

|

|

|

|

| 22 | 1C | IF1 Message Control | NewDat, UMask, EoB, DLC=4 |

| 9084 |

|

|

|

|

|

|

|

|

|

| 23 | 1E | IF1 Message Data A1 |

|

| FACE |

|

|

|

|

|

|

|

|

|

| 24 | 20 | IF1 Message Data A2 | some bytes for initialisation |

| B055 |

|

|

|

|

|

|

|

| |

about.fm | 25 | 22 | IF1 Message Data B1 |

| FEED |

| |

|

|

| |||||

|

|

|

|

|

|

| |

26 | 24 | IF1 Message Data B2 |

|

| CAFE |

| |

_ |

|

|

|

|

|

|

|

manual | 27 | 10 | IF1 Command Request | Ref_Msg in message object 1 |

| 0001 |

|

|

|

| |||||

|

|

|

|

|

|

|

|

| 28 | 16 | IF1 Mask2 | all bits must match |

| FFFF |

|

|

|

|

|

|

|

|

|

| 29 | 1A | IF1 Arbitration2 | MsgVal, Dir =Tx, xx_Msg2 id | AC08 | AC48 | AC88 |

|

|

|

|

|

|

|

|

| 30 | 1C | IF1 Message Control | NewDat, EoB, DLC=8 |

| 8088 |

|

|

|

|

|

|

|

|

|

| 31 | 10 | IF1 Command Request | xx_Msg2 in message object 2 |

| 0002 |

|

|

|

|

|

|

|

| |

| 32 | 1A | IF1 Arbitration2 | MsgVal, Dir =Tx, xx_Msg3 id | AC0C | AC4C | AC8C |

|

|

|

|

|

|

|

|

| 33 | 10 | IF1 Command Request | xx_Msg3 in message object 3 |

| 0003 |

|

|

|

|

|

|

|

|

|

| 34 | 1A | IF1 Arbitration2 | MsgVal, Dir =Tx, M1_Msg4 id | 0000 | AC50 | 0000 |

|

|

|

|

|

|

|

|

| 35 | 10 | IF1 Command Request | M1_Msg4 in message object 4 |

| 0004 |

|

|

|

|

|

|

|

|

|

| 36 | 1A | IF1 Arbitration2 | not valid, Dir =Tx, dummy id |

| 4FFF |

|

|

|

|

|

|

|

|

|

BOSCH | - 71/77 - | 11.11.02 |