TTCAN | User’s Manual | Revision 1.6 |

manual_about.fm

EECS | Enable External Clock Synchronisation | |

| one | TUR Configuration (NumCfg only) may be updated during |

|

| TTCAN operation. |

| zero | TUR Configuration may not be updated. |

TTMode | TTCAN Operation Mode | |

| 0x0 | TTMode_0 Event driven CAN Communication (default mode). |

| 0x1 | TTMode_1 Configuration Mode. |

| 0x2 | TTMode_2 Strictly Time Triggered Operation. |

| 0x3 | TTMode_3 Event Synchronised Time Triggered Operation. |

Note : The CPU may write to the TT Operation Mode register only during initialisation (Init and CCE are set). Configuration Mode enables the write access to the other TTCAN configuration regis- ters. The whole CAN module remains in initialisation mode while TTMode is TTMode_1, “Con- figuration Mode”, even if Init is reset.

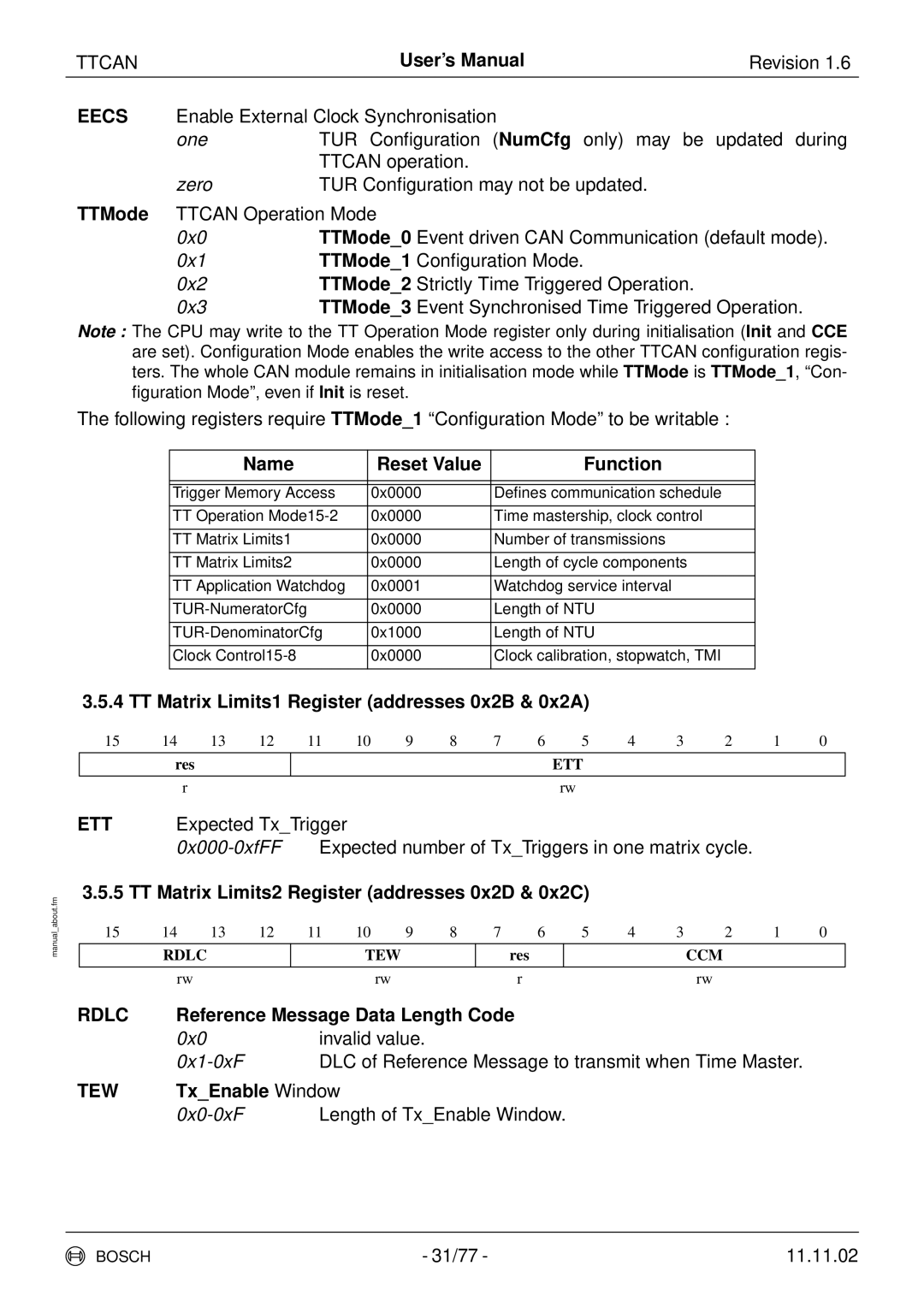

The following registers require TTMode_1 “Configuration Mode” to be writable :

|

|

|

| Name |

|

|

| Reset Value |

|

| Function |

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

| Trigger Memory Access |

| 0x0000 |

| Defines communication schedule |

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

| TT Operation |

| 0x0000 |

| Time mastership, clock control |

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

| TT Matrix Limits1 |

|

| 0x0000 |

| Number of transmissions |

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

| TT Matrix Limits2 |

|

| 0x0000 |

| Length of cycle components |

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

| TT Application Watchdog |

| 0x0001 |

| Watchdog service interval |

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

| 0x0000 |

| Length of NTU |

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

| 0x1000 |

| Length of NTU |

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

| Clock |

|

| 0x0000 |

| Clock calibration, stopwatch, TMI |

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

| |||||||||

3.5.4 TT Matrix Limits1 Register (addresses 0x2B & 0x2A) |

|

|

|

|

| |||||||||||||

15 | 14 | 13 | 12 |

| 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| res |

|

|

|

|

|

|

|

|

|

| ETT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| r |

|

|

|

|

|

|

|

|

|

| rw |

|

|

|

|

|

ETT Expected Tx_Trigger

3.5.5 TT Matrix Limits2 Register (addresses 0x2D & 0x2C)

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 |

| 5 | 4 | 3 | 2 | 1 | 0 | |

|

| RDLC |

|

|

| TEW |

|

| res |

|

|

|

|

| CCM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| rw |

|

|

| rw |

|

| r |

|

|

|

|

| rw |

|

|

RDLC | Reference Message Data Length Code |

|

|

|

|

|

|

|

| ||||||||

|

| 0x0 |

|

| invalid value. |

|

|

|

|

|

|

|

|

|

| ||

|

|

| DLC of Reference Message to transmit when Time Master. |

| |||||||||||||

TEW | Tx_Enable Window |

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

| Length of Tx_Enable Window. |

|

|

|

|

|

| ||||||||

BOSCH | - 31/77 - | 11.11.02 |