TTCAN | User’s Manual | Revision 1.6 |

manual_about.fm

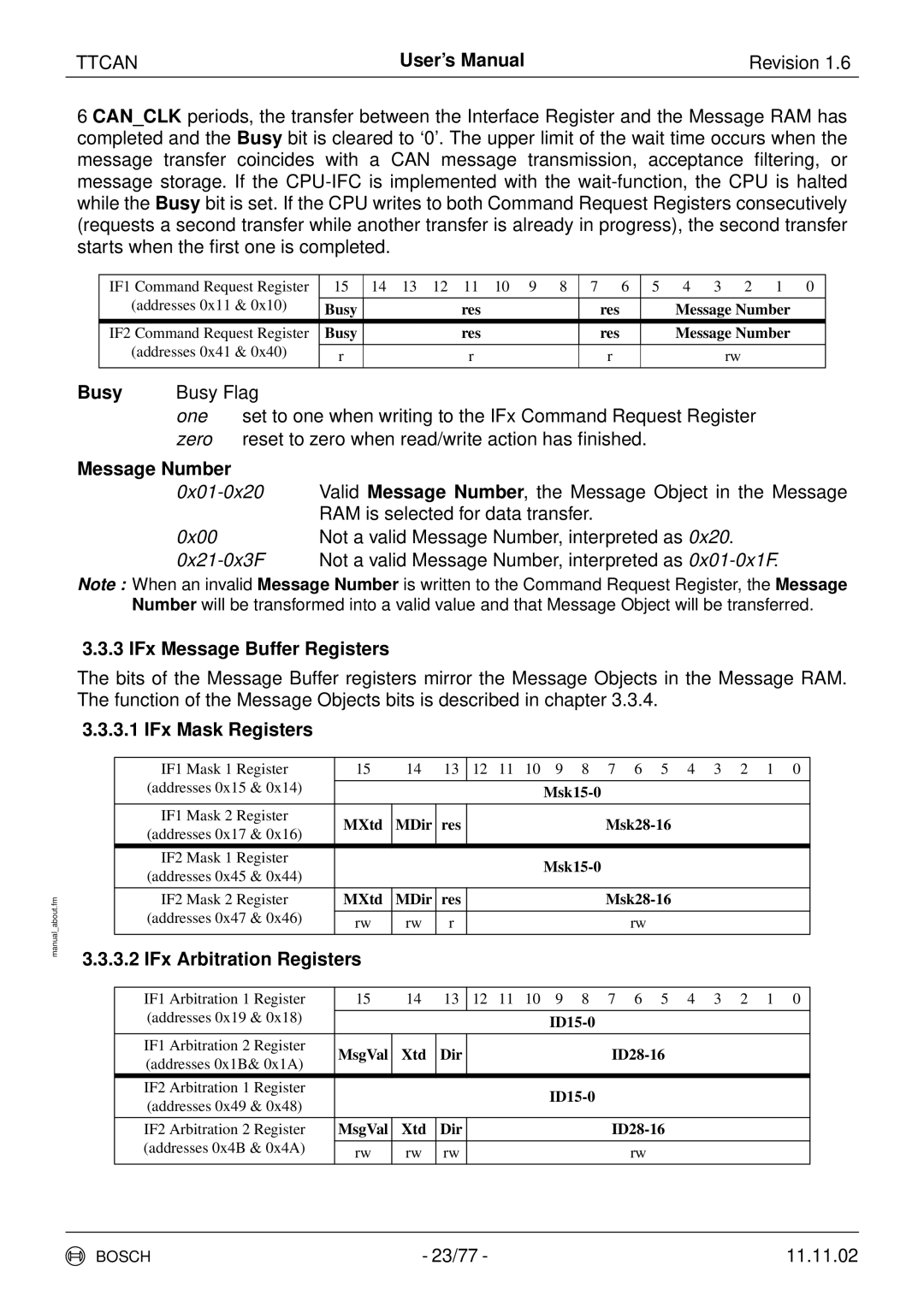

6 CAN_CLK periods, the transfer between the Interface Register and the Message RAM has completed and the Busy bit is cleared to ‘0’. The upper limit of the wait time occurs when the message transfer coincides with a CAN message transmission, acceptance filtering, or message storage. If the

| IF1 Command Request Register | 15 | 14 | 13 12 11 10 9 8 | 7 6 | 5 | 4 3 2 1 0 | ||

|

| (addresses 0x11 & 0x10) |

|

|

|

|

|

| |

|

| Busy |

| res | res |

| Message Number | ||

|

|

|

|

|

|

|

| ||

| IF2 Command Request Register | Busy |

| res | res |

| Message Number | ||

|

| (addresses 0x41 & 0x40) |

|

|

|

|

|

| |

|

| r |

| r | r |

| rw | ||

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| |

Busy | Busy Flag |

|

|

|

|

|

| ||

|

| one | set to one when writing to the IFx Command Request Register | ||||||

|

| zero reset to zero when read/write action has finished. |

| ||||||

Message Number

0x00Not a valid Message Number, interpreted as 0x20.

Note : When an invalid Message Number is written to the Command Request Register, the Message Number will be transformed into a valid value and that Message Object will be transferred.

3.3.3 IFx Message Buffer Registers

The bits of the Message Buffer registers mirror the Message Objects in the Message RAM. The function of the Message Objects bits is described in chapter 3.3.4.

3.3.3.1 IFx Mask Registers

IF1 Mask 1 Register | 15 | 14 | 13 | 12 11 10 9 8 7 6 5 4 3 2 1 0 | |

(addresses 0x15 & 0x14) |

|

|

|

| |

|

|

| |||

|

|

|

|

| |

IF1 Mask 2 Register | MXtd | MDir | res | ||

(addresses 0x17 & 0x16) | |||||

|

|

|

| ||

|

|

|

|

| |

IF2 Mask 1 Register |

|

|

| ||

(addresses 0x45 & 0x44) |

|

|

| ||

|

|

|

| ||

|

|

|

|

| |

IF2 Mask 2 Register | MXtd | MDir | res | ||

(addresses 0x47 & 0x46) |

|

|

|

| |

rw | rw | r | rw | ||

| |||||

|

|

|

|

|

3.3.3.2 IFx Arbitration Registers

IF1 Arbitration 1 Register | 15 | 14 | 13 | 12 11 | 10 9 8 7 6 5 4 3 2 1 0 |

(addresses 0x19 & 0x18) |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

IF1 Arbitration 2 Register | MsgVal | Xtd | Dir |

| |

(addresses 0x1B& 0x1A) |

| ||||

|

|

|

|

| |

|

|

|

|

|

|

IF2 Arbitration 1 Register |

|

|

|

| |

(addresses 0x49 & 0x48) |

|

|

|

| |

|

|

|

|

| |

|

|

|

|

|

|

IF2 Arbitration 2 Register | MsgVal | Xtd | Dir |

| |

(addresses 0x4B & 0x4A) |

|

|

|

|

|

rw | rw | rw |

| rw | |

|

| ||||

|

|

|

|

|

|

BOSCH | - 23/77 - | 11.11.02 |