CY7C67200

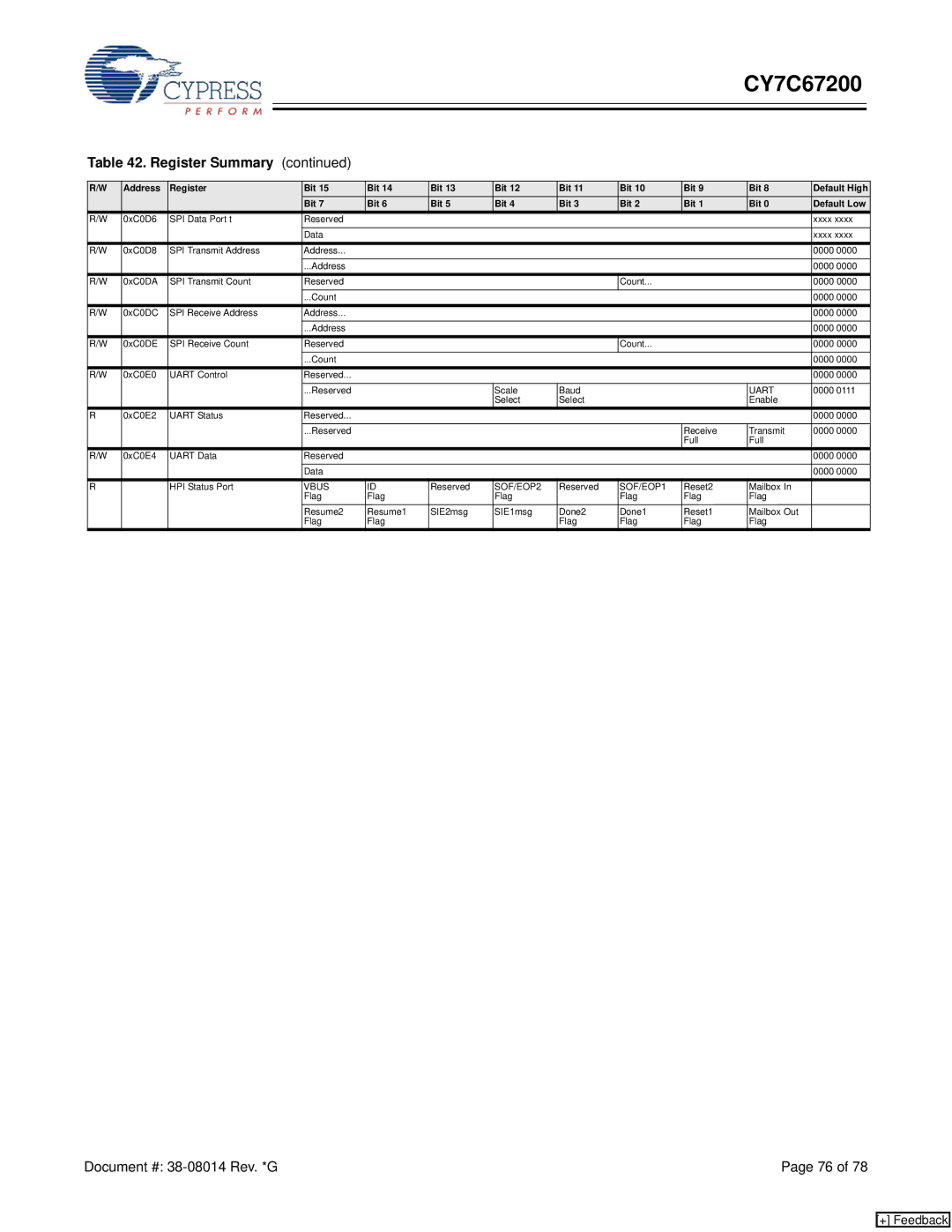

Table 42. Register Summary (continued)

R/W | Address | Register | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Default High |

|

|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default Low |

R/W | 0xC0D6 | SPI Data Port t | Reserved |

|

|

|

|

|

|

| xxxx xxxx |

|

|

| Data |

|

|

|

|

|

|

| xxxx xxxx |

R/W | 0xC0D8 | SPI Transmit Address | Address... |

|

|

|

|

|

|

| 0000 0000 |

|

|

| ...Address |

|

|

|

|

|

|

| 0000 0000 |

R/W | 0xC0DA | SPI Transmit Count | Reserved |

|

|

|

| Count... |

|

| 0000 0000 |

|

|

| ...Count |

|

|

|

|

|

|

| 0000 0000 |

R/W | 0xC0DC | SPI Receive Address | Address... |

|

|

|

|

|

|

| 0000 0000 |

|

|

| ...Address |

|

|

|

|

|

|

| 0000 0000 |

R/W | 0xC0DE | SPI Receive Count | Reserved |

|

|

|

| Count... |

|

| 0000 0000 |

|

|

| ...Count |

|

|

|

|

|

|

| 0000 0000 |

R/W | 0xC0E0 | UART Control | Reserved... |

|

|

|

|

|

|

| 0000 0000 |

|

|

| ...Reserved |

|

| Scale | Baud |

|

| UART | 0000 0111 |

|

|

|

|

|

| Select | Select |

|

| Enable |

|

R | 0xC0E2 | UART Status | Reserved... |

|

|

|

|

|

|

| 0000 0000 |

|

|

| ...Reserved |

|

|

|

|

| Receive | Transmit | 0000 0000 |

|

|

|

|

|

|

|

|

| Full | Full |

|

R/W | 0xC0E4 | UART Data | Reserved |

|

|

|

|

|

|

| 0000 0000 |

|

|

| Data |

|

|

|

|

|

|

| 0000 0000 |

R |

| HPI Status Port | VBUS | ID | Reserved | SOF/EOP2 | Reserved | SOF/EOP1 | Reset2 | Mailbox In |

|

|

|

| Flag | Flag |

| Flag |

| Flag | Flag | Flag |

|

|

|

| Resume2 | Resume1 | SIE2msg | SIE1msg | Done2 | Done1 | Reset1 | Mailbox Out |

|

|

|

| Flag | Flag |

|

| Flag | Flag | Flag | Flag |

|

Document #: | Page 76 of 78 |

[+] Feedback