CY7C67200

Receive Bit Length (Bits [2:0])

The Receive Bit Length field controls whether a full byte or partial byte will be received. If Receive Bit Length is ‘000’ then a full byte will be received. If Receive Bit Length is ‘001’ to ‘111’, then the value indicates the number of bits that will be received.

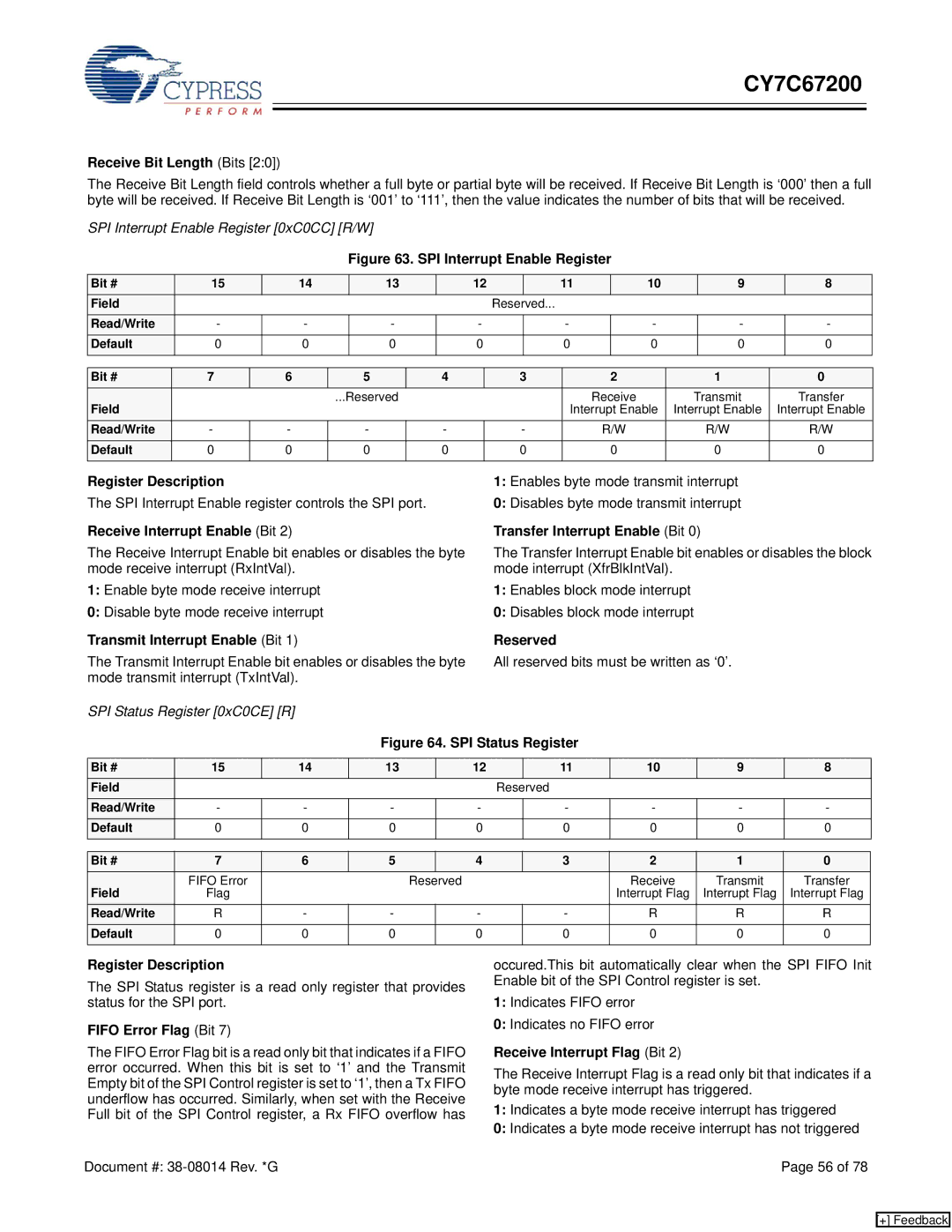

SPI Interrupt Enable Register [0xC0CC] [R/W]

Figure 63. SPI Interrupt Enable Register

Bit # | 15 | 14 | 13 | 12 |

| 11 | 10 | 9 | 8 |

Field |

|

|

|

| Reserved... |

|

|

| |

Read/Write | - | - | - | - |

| - | - | - | - |

Default | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Field |

|

| ...Reserved |

|

| Receive | Transmit | Transfer |

|

|

|

|

| Interrupt Enable | Interrupt Enable | Interrupt Enable | |

Read/Write | - | - | - | - | - | R/W | R/W | R/W |

Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

Register Description

The SPI Interrupt Enable register controls the SPI port.

Receive Interrupt Enable (Bit 2)

The Receive Interrupt Enable bit enables or disables the byte mode receive interrupt (RxIntVal).

1:Enable byte mode receive interrupt

0:Disable byte mode receive interrupt

Transmit Interrupt Enable (Bit 1)

The Transmit Interrupt Enable bit enables or disables the byte mode transmit interrupt (TxIntVal).

1:Enables byte mode transmit interrupt

0:Disables byte mode transmit interrupt

Transfer Interrupt Enable (Bit 0)

The Transfer Interrupt Enable bit enables or disables the block mode interrupt (XfrBlkIntVal).

1:Enables block mode interrupt

0:Disables block mode interrupt

Reserved

All reserved bits must be written as ‘0’.

SPI Status Register [0xC0CE] [R]

Figure 64. SPI Status Register

Bit # | 15 | 14 | 13 | 12 |

| 11 | 10 | 9 | 8 |

Field |

|

|

|

| Reserved |

|

|

| |

Read/Write | - | - | - | - |

| - | - | - | - |

Default | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

Bit # | 7 | 6 | 5 |

| 4 | 3 | 2 | 1 | 0 |

Field | FIFO Error |

| Reserved |

|

| Receive | Transmit | Transfer | |

Flag |

|

|

|

|

| Interrupt Flag | Interrupt Flag | Interrupt Flag | |

Read/Write | R | - | - |

| - | - | R | R | R |

Default | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

Register Description

The SPI Status register is a read only register that provides status for the SPI port.

FIFO Error Flag (Bit 7)

The FIFO Error Flag bit is a read only bit that indicates if a FIFO error occurred. When this bit is set to ‘1’ and the Transmit Empty bit of the SPI Control register is set to ‘1’, then a Tx FIFO underflow has occurred. Similarly, when set with the Receive Full bit of the SPI Control register, a Rx FIFO overflow has

occured.This bit automatically clear when the SPI FIFO Init Enable bit of the SPI Control register is set.

1:Indicates FIFO error

0:Indicates no FIFO error

Receive Interrupt Flag (Bit 2)

The Receive Interrupt Flag is a read only bit that indicates if a byte mode receive interrupt has triggered.

1:Indicates a byte mode receive interrupt has triggered

0:Indicates a byte mode receive interrupt has not triggered

Document #: | Page 56 of 78 |

[+] Feedback