CY7C67200

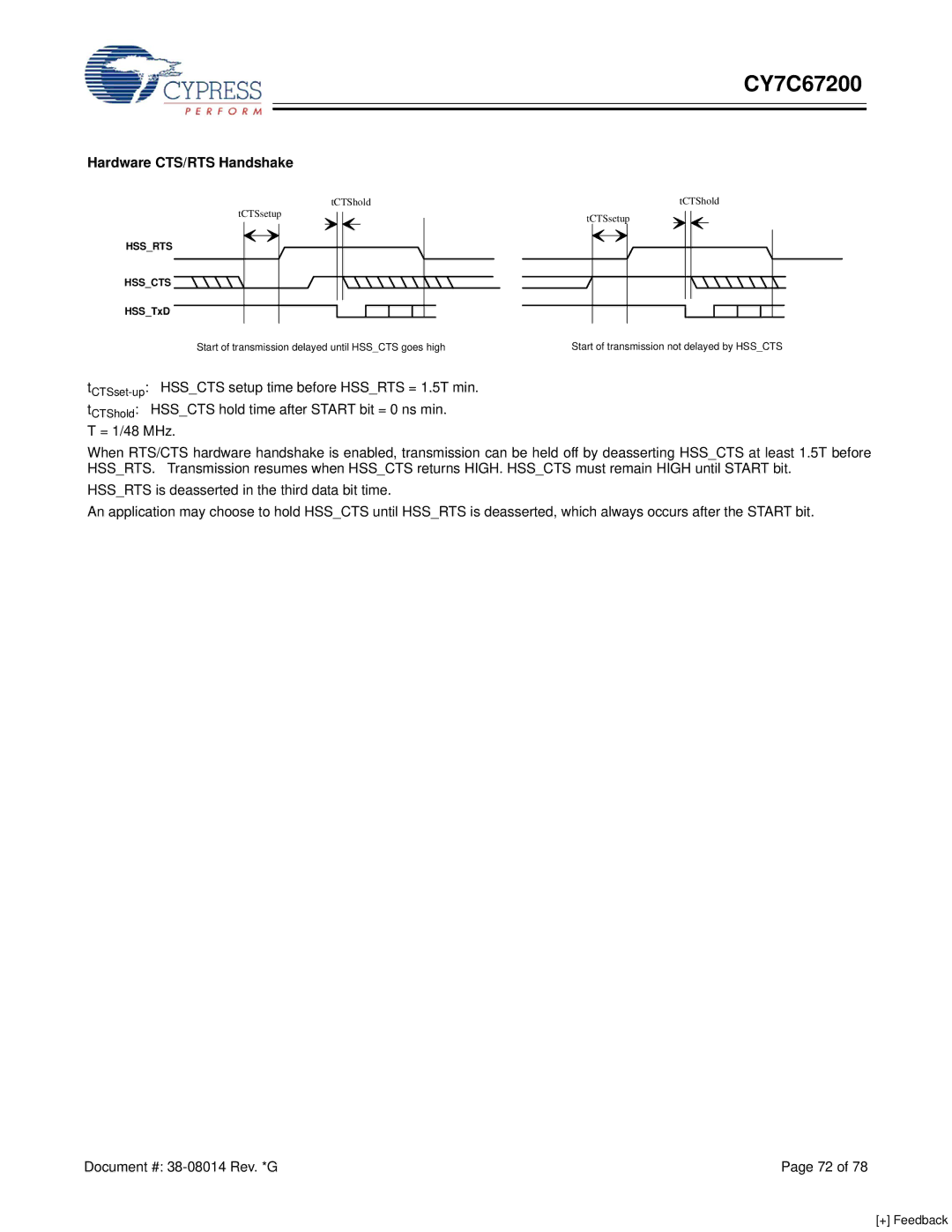

Hardware CTS/RTS Handshake

tCTShold

tCTSsetup

HSS_RTS

HSS_CTS

HSS_TxD

Start of transmission delayed until HSS_CTS goes high

tCTShold

tCTSsetup

Start of transmission not delayed by HSS_CTS

tCTShold: HSS_CTS hold time after START bit = 0 ns min. T = 1/48 MHz.

When RTS/CTS hardware handshake is enabled, transmission can be held off by deasserting HSS_CTS at least 1.5T before HSS_RTS. Transmission resumes when HSS_CTS returns HIGH. HSS_CTS must remain HIGH until START bit.

HSS_RTS is deasserted in the third data bit time.

An application may choose to hold HSS_CTS until HSS_RTS is deasserted, which always occurs after the START bit.

Document #: | Page 72 of 78 |

[+] Feedback