CY7C67200

USB Interface

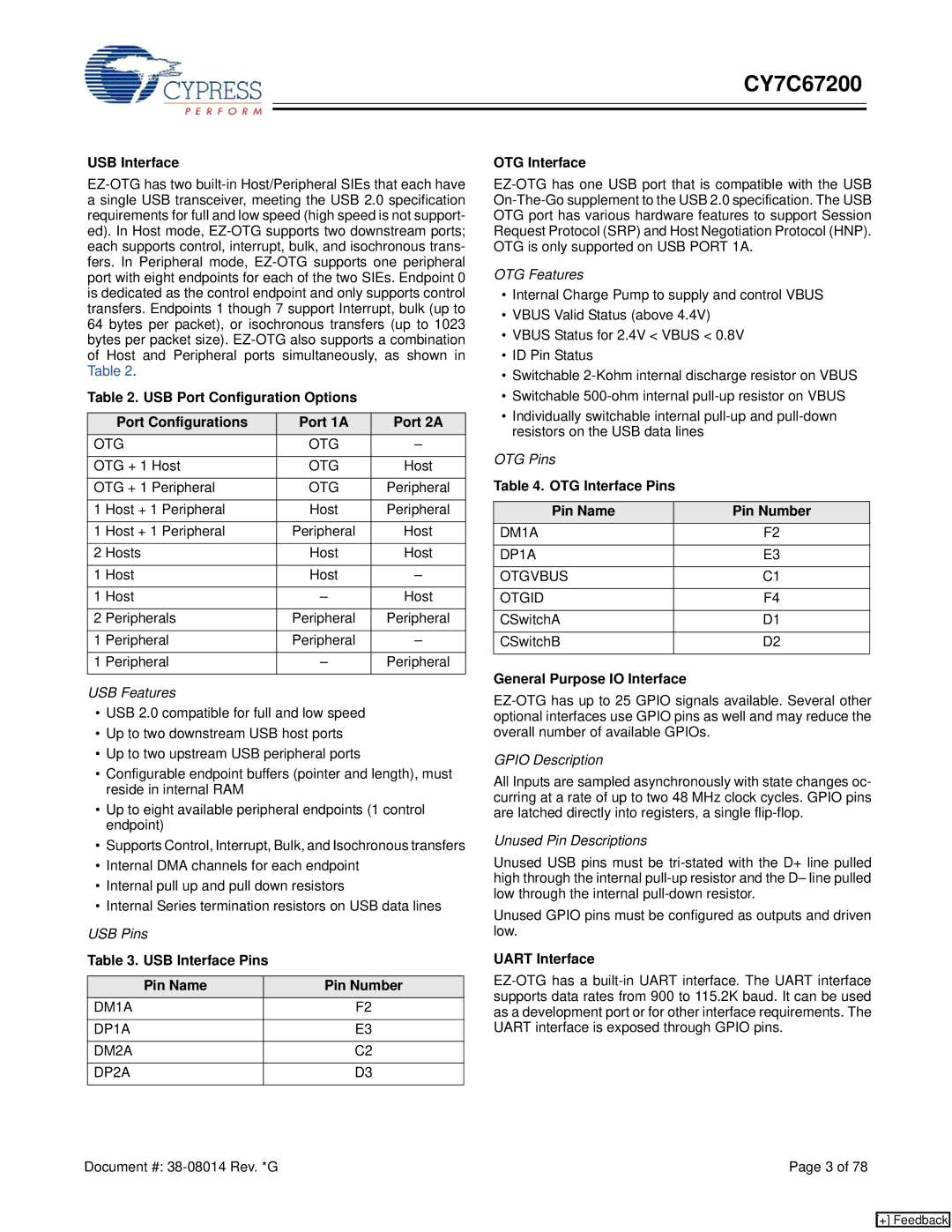

Table 2. USB Port Configuration Options

| Port Configurations | Port 1A | Port 2A |

OTG | OTG | – | |

|

|

| |

OTG + 1 Host | OTG | Host | |

|

|

| |

OTG + 1 Peripheral | OTG | Peripheral | |

|

|

|

|

1 | Host + 1 Peripheral | Host | Peripheral |

|

|

|

|

1 | Host + 1 Peripheral | Peripheral | Host |

|

|

|

|

2 | Hosts | Host | Host |

|

|

|

|

1 | Host | Host | – |

|

|

|

|

1 | Host | – | Host |

|

|

|

|

2 | Peripherals | Peripheral | Peripheral |

|

|

|

|

1 | Peripheral | Peripheral | – |

|

|

|

|

1 | Peripheral | – | Peripheral |

|

|

|

|

USB Features

•USB 2.0 compatible for full and low speed

•Up to two downstream USB host ports

•Up to two upstream USB peripheral ports

•Configurable endpoint buffers (pointer and length), must reside in internal RAM

•Up to eight available peripheral endpoints (1 control endpoint)

•Supports Control, Interrupt, Bulk, and Isochronous transfers

•Internal DMA channels for each endpoint

•Internal pull up and pull down resistors

•Internal Series termination resistors on USB data lines

USB Pins

Table 3. USB Interface Pins

Pin Name | Pin Number |

DM1A | F2 |

|

|

DP1A | E3 |

|

|

DM2A | C2 |

|

|

DP2A | D3 |

|

|

OTG Interface

OTG Features

•Internal Charge Pump to supply and control VBUS

•VBUS Valid Status (above 4.4V)

•VBUS Status for 2.4V < VBUS < 0.8V

•ID Pin Status

•Switchable

•Switchable

•Individually switchable internal

OTG Pins

Table 4. OTG Interface Pins

Pin Name | Pin Number |

DM1A | F2 |

|

|

DP1A | E3 |

|

|

OTGVBUS | C1 |

|

|

OTGID | F4 |

|

|

CSwitchA | D1 |

|

|

CSwitchB | D2 |

|

|

General Purpose IO Interface

GPIO Description

All Inputs are sampled asynchronously with state changes oc- curring at a rate of up to two 48 MHz clock cycles. GPIO pins are latched directly into registers, a single

Unused Pin Descriptions

Unused USB pins must be

Unused GPIO pins must be configured as outputs and driven low.

UART Interface

Document #: | Page 3 of 78 |

[+] Feedback