Page

Fujitsu DL3700 Pro/3800 Pro

Page

Bescheinigung des Herstellers/Importeurs

CE Declaration

Energy Saving

DOT Matrix Printer

Manufacturers Declaration of Conformity

Trademark Acknowledgement

Options

Printer Models

Vii

Organization

Indicated as follows

Viii

Users

Table of Contents

General Tips Multipart Forms Envelopes

Switching to Single Sheets Switching to Continuous Forms

DPL24C Plus Organization

Using Setup Mode

Xii

Installing the Cut Sheet Feeder Installing the Color Kit

Compatible Mode Nibble Mode Data Transmission Timing

Factory Default Settings

Serial Options Cable Wiring Serial Protocols

GL-1

Xiv

Control panel

Quick Reference

Quick Reference

Printer Operations Normal Mode

Dot matrix printer

Features

Introduction

Cut sheet feeder

Options

Introduction

Location

Selecting a Good

Setting UP

Checking items received

Unpacking the Printer

Removing the shipping restraint cardboard

Checking Options and Supplies

Installing the cut sheet stand

Installing the Cut Sheet Stand

Preparing to install the ribbon

Preparing the ribbon cartridge

Installing the ribbon cartridge

With Your Printer

Getting Acquainted

Printer components front and right

Printer components rear

Connecting the Power

Cord

Connecting the power cord

Offline

Testing the Printer

Loading a sheet of paper

Printing the Self-Test

Starting the self-test

Sample self-test

Setting UP

Demo pattern

Selecting a Parallel Interface Cable

Opening the shutter

Connecting the interface cable

For Experienced Users

Selecting AN Emulation

Turn the printer on and load a sheet of paper

Enter setup mode

Initial printout in setup mode

Select an emulation

Select the MENU1 function

Exit MENU1

Exit setup mode to save the emulation

Setting UP

Using MS-DOS to Specify Serial Interface Settings

Mode LPT1=COM1

Setting UP

Selecting Paper

Paper Handling

Overview of Paper

Paper Handling

Operations

Printer levers and buttons

Lever/Button Purpose Action

Levers and Buttons Used for Paper Handling

LF/FF

Tear OFF

Adjusting the paper thickness lever

Adjusting for Paper

Thickness

Using Single Sheets

Paper Thickness Lever Settings

Number of Copies Setting *2 Including the Original *1

Move the lever one setting higher

Preparing to load a sheet of paper

Adjusting the left margin

Load

Loading Paper in the Cut Sheet Feeder Option

Preparing the cut sheet feeder ASF300

Preparing the cut sheet feeder ASF100

Adjusting the left margin

Loading the cut sheet feeder ASF300

Loading the cut sheet feeder ASF100

Forms

Using Continuous

Bad placement

Good placement

Placement of continuous forms

Positioning the Paper Stack

Preparing to load continuous forms paper

Loading Continuous Forms Push Tractor and Rear Feed

Positioning the tractors Adjusting the left margin

Lowering the cut sheet stand

Adjusting paper tension

Loading Continuous Forms Pull Tractor and Bottom Feed

Removing the bail roller unit

Removing the tractor unit

Installing the tractor unit for pull-tractor feed

Opening the two holders

Passing continuous forms paper from under the printer

Setting continuous forms paper on the tractors

Unloading Continuous Forms

Tearing off continuous forms

Feeding and Positioning Paper

Micro Feed

Failure to retract the forms paper will cause paper jams

Switching to Single Sheets

General Tips

Tips on Paper Handling

Labels

Paper Handling

Printing

Printing

Using Commercial Software

Printer control panel

Selecting MENU1 or MENU2

MENU1 MENU2

MENU1 and MENU2 Settings

Draft

Prestg

Hidrft

Menu Font

Starting or Stopping Printing

Locking the selected resident font

Stopping Printing

Printing the remaining lines on a

Continuing printing after supplying paper

Removing Single Sheets

Buffer

Clearing the Print

Using Setup Mode

Entering Setup Mode

Using Setup Mode

Entering setup mode

Function Purpose

Setup Mode Functions

List

Default

SELF-TST

HEX-DUMP

Select the MENU2 function

Load continuous forms paper Enter setup mode

Almnt

Summary of setup mode

Select the current emulation

Exit setup mode, saving the new font and pitch

Change the font to Prestige Elite

Select the current print quality

Setup Mode

Printing a List

Use the printer tear-off feature Tear OFF button

Selected Options

Select the List function

Printout of factory defaults using List

To Change

Deciding Which Options

Required Options

See the section Changing Configuration

Adjustment Options later in this

See the section Changing Hardware

See the section Changing Print Position

Using Setup Mode

MENU1 and MENU2 Items and Options

Quality

Font TIMLS-N TIMLS-B TIMLS-I DOWNLD#

Letter

Report

Lpi Lpi double spacing

Attrib

CHAR-H

None Italics Condnsd Shadow Bold

Autosel

Color

Black

Yellow

## Colm

LFT-END

TOP-MRG

## Line

USA

Languge

German

Swedish

SLOV-T

Languge Slov

Polish

POLSH-T

Italian

Languge French

Spanish

DANISH1

SET

CHR-SET

Italic

Graphic

Disable

Enable

Width

Zerofnt

LF & CR

LF-CODE LF only

Rghtend Wrap

OVR-PRT

Select the MENU1 or MENU2 function

Exit MENU1 or MENU2

PPR-OUT setting

Indicator lights red, regardless

Hardwre Items and Options

Options Description Items

Print buffer Download buffer

Only for graphics application

0BYTE option is recommended

With 128KB selected, the printer

Cannot accept any download font

DTR

XON/XOF

REV-CHL

DSR Ignore

Select an option for the selected item

Select the Hardwre function

Changing Print Position Adjustment Options

Options Description

Adjust Items and Options

CUT-LFT

CNT-LFT

CUT-ADJ

Exit the Adjust function

Select the Adjust function

Select an option from 1/6IN to 66/6IN

Config Items and Options

Changing Configuration Options

Exit setup mode, saving the top-of-form setting

Check the top-of-form setting

Positioning will fail if

Length setting does not match

Actual perforation spacing

Button

Cutload

Loadtim

Decode

Areacnt

Setup

ON-LOAD

Offline

Tractor

CONT-PE

Edge

Exit the Config function

Select the Config function

Select an option

Select the SAVE/END function

Print the Function menu

Resetting Power-On Defaults

Resetting Defaults

Select the Default function

Using the Diagnostic

Functions

Printing the Self-Test

Examine the self-test

Select the SELF-TST function

Exit the SELF-TST function

Print the hex dump

Select the HEX-DUMP function

Exit the HEX-DUMP function

Sample hex dump

Checking Vertical Print Alignment V-ALMNT

Adjust the vertical print alignment at correspondence speed

Adjust the vertical print alignment at letter quality speed

Adjust the vertical print alignment at draft speed

Select the V-ALMNT function

To exit the V-ALMNT function, you must exit setup mode

Setup Mode Reference

Correct vertical print alignment

Exit the V-ALMNT function

Setup Mode Functions Items & Options Online

Setup

Differences in IBM Proprinter XL24E Emulation

Japan

Online Setup Mode

Cleaning and Vacuuming the Printer

Cleaning

Printer interior

Maintenance

Rubber to harden

Replacing the Ribbon

Removing the ribbon cartridge

Paper thickness lever

Preparing the new ribbon cartridge

Installing the new ribbon cartridge

Replacing the print head

Maintenance

Print Quality Problems

Solving Problems

Print Quality Problems and Solutions

TROUBLE-SHOOTING

Problem Solution

Ing an Emulation in Chapter

Section Changing MENU1 and MENU2

Using the Diagnostic Functions in Chapter

Changing MENU1 and MENU2 Options

Paper Handling Problems and Solutions

TROUBLE-SHOOTING

Tips for clearing a jammed sheet from the printer

Common cause of abnormal paper feeding

Operating Problems and Solutions

Ing Hardware Options in Chapter

Printer Failures

Error Font indicators lit

COUR10

PRESTG12

Diagnostic Functions Getting Help

TROUBLE-SHOOTING

Single bin cut sheet feeder

Installing the CUT Sheet Feeder

Installing the Color KIT

Installing Options

Color kit ribbon shift unit

Seven colors are printed by command

Installing Options

Supplies Order Number

Supplies Options

Option Order Number Description

Supplies and Options

Physical Specifications

Functional Specifications

Printer and Paper Specifications

Paper thickness

Command sets emulations

Paper length

Number of copies

Performance Specifications

Form feed speed

Line feed speed

Ribbon life

Certification

Print area for single sheets

Paper Specifications

Print area for continuous forms

Type of Paper Number of Parts Thickness

Do not use in high humidity environments

Printer and Paper Specifications

Command Sets

Function Command Print Mode Control

Command Sets DPL24C Plus

Fujitsu DPL24C Plus

Function Command

Command Sets

ESC M

Horizontal Control

ESC P

ESC LF

Vertical Control

NUL

Function Command Tabulation

Formatting

ESC O

Character Set Control

Color Selection

Font Selection and Downloading

Word Processing

Bit Selection of font

Bit Print quality

= 0 = 1

Quality Spacing Pitch Point Typeface

Bit Font number selection Remarks

Bit Font quality selection

Cut Sheet Feeder Control

Function Command Bit Image Graphics

Initialize Printer

Bar Code Printing

Ascii

Selectable options in setup mode Command

SHADOW, Bold

NONE, ITALICS, Condnsd

ESC E ESC F

ESC G ESC H

ESC7

DC3 ENABLE, Disable

ESC6

SKIP, NO-SKIP ESC N ESC O

DC4

IBM Proprinter XL24E Emulation

Height Spacing

DC2

Command Sets IBM XL24E

ESC T

ESC B NUL

ESC D NUL

Code page ID

Function Command Color Selection

ESC Q #

Miscellaneous

Function Command Downloading

BEL

Epson ESC/P2

Command Sets ESC/P2

Emulation

Space Backspace Carriage return Set elite pitch

ESC D

× 256/360*1 inch

Function Command Color Selection

DEL

≤ character codes ≤

Command Sets ESC/P2

Graphics type m graphics ESC * m n1 n2

Command Sets ESC/P2

Parallel Interface

Unidirectional forward channel mode or conventional mode

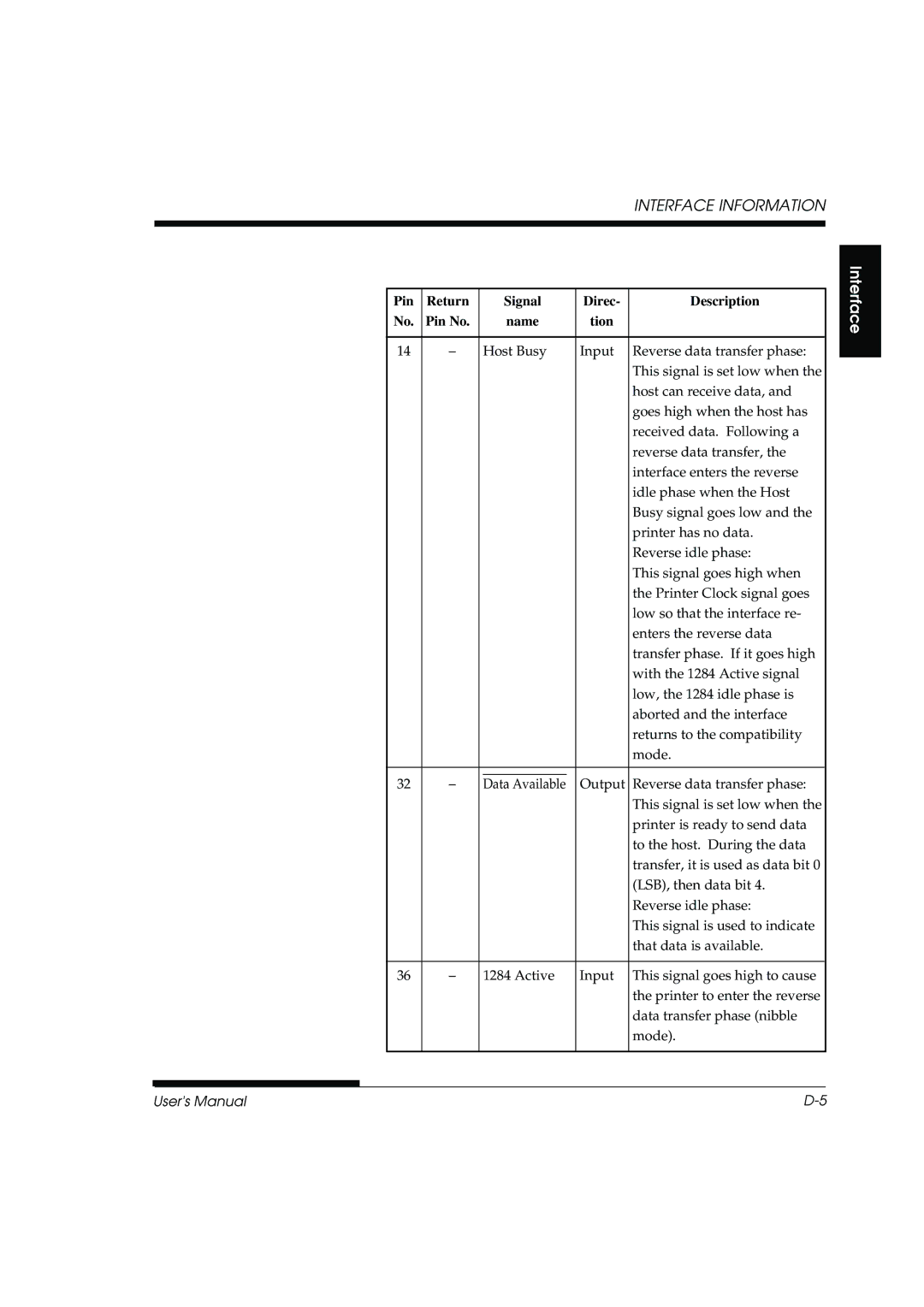

Pin Return Signal Direc Description Pin No

Compatible Mode

Interface Information

Tion

Direc Description Pin No

Pin Return

Slct

Inprm

Pin Return Signal Direc Description Pin No Name

Name Tion

Busy

Serial Interface

Pin Signal Direc Description Name

RTS

CTS

Serial Options

DSR

XON/XOFF

Protocol Description

Code Page 437 Character Set

Character Sets 1 DPL24C Plus and Ibmê XL24E Emulation

Italic and Graphics

Character Sets

Character Sets ESC/P2

Italic Character Set

Character

National Character Sets ALL Emulations

PAGE852/PG852-T Code PAGE855 Code

PAGE865 Code Page 865Nordic PAGE866 Code Page 866Cyrillic

PAGE860 Code Page 860Portugal

POLISH/POLSH-T Polish MAZOWIA/MAZOW-T Mazowian

HUNGARY/HUNG-T Hungarian SLOV/SLOV-T Slovenian

Character Sets

ELOT928 Elot PG-DHN Code Page DHN

IBM437 IBM IBM851 IBM

Character Sets

Macedon Macedonian

MIK

ABG

Decgr

PG-MAC

HBR DEC

PAGE862

National Character Sets DPL24C Plus and IBM XL24E Emulation

ESC/P2 Emulation

DANISH1/NORWEGN Danish1/Norwegian DANISH2 Danish2

DANISH1

Danish1 SPANSH1 Spanish1

Character Sets

DANISH2 Danish2 Korea Korea

Norwegn Norwegian French French

National Character

Legal Legal

Sets and Supported

Resident Fonts ALL

ECMA94

National Name Character set Setup menu

PAGE852

PAGE855

MIK

Resident font National Name Character set Setup menu

ABG ABY

PG-MAC

OCR-B OCR-A

Resident Fonts

Courier Scalable Normal Bold Italic

Resident Fonts

Bold Italic Timeless Scalable Normal

Ascii

A4 size Application software

Baud rate Bidirectional printing Bit Bottom feed Buffer

Glossary of Terms

Commonly used fonts

Offline Online

Interface

GL-5

Self-test

Setup mode

Separator

Serial interface

Top-of-form TOF Tractor feed Unidirectional printing

Top margin

GL-8

Index

CR-CODE

Index

SELF-TST Almnt

Menu

Power

Ribbon subcassette A-1 RS-232C serial interface

Others

IN-8

Fujitsu Canada INC

C147-E042-05EN