: PX JQWa

BIOS Addresses

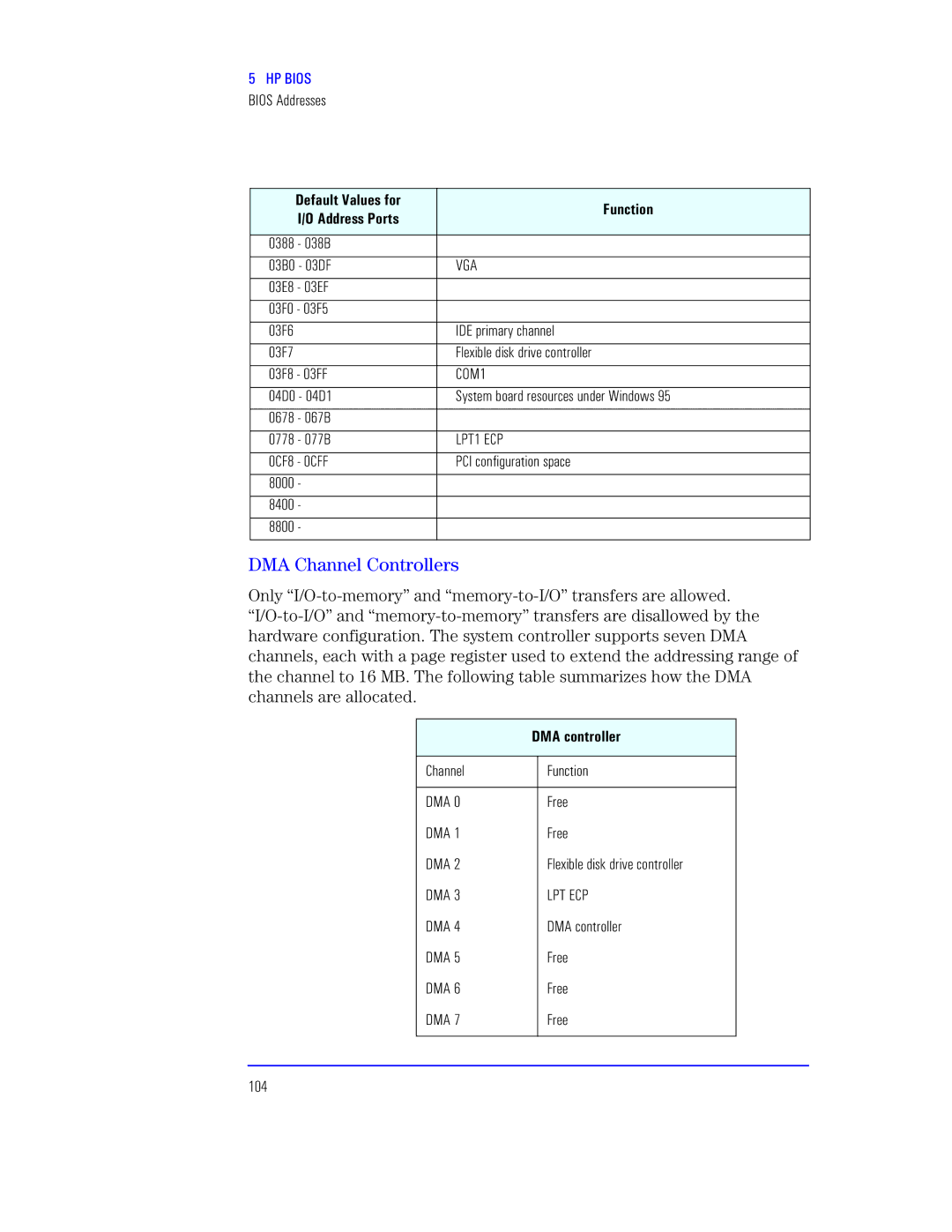

| Mtup dp®t u | Or |

| R4Y Jsst | |

|

| |

|

|

|

0388 | - 038B |

|

|

| |

03B0 - 03DF | VGA | |

|

| |

03E8 - 03EF |

| |

|

|

|

03F0 | - 03F5 |

|

|

|

|

03F6 |

| IDE primary channel |

|

|

|

03F7 |

| Flexible disk drive controller |

|

|

|

03F8 | - 03FF | COM1 |

|

| |

04D0 - 04D1 | System board resources under Windows 95 | |

|

|

|

0678 | - 067B |

|

|

|

|

0778 | - 077B | LPT1 ECP |

|

| |

0CF8 - 0CFF | PCI configuration space | |

|

|

|

8000 | - |

|

|

|

|

8400 | - |

|

|

|

|

8800 | - |

|

|

|

|

TeQ Sz

Only

| MVJ r®®t | |

|

|

|

Channel |

| Function |

|

|

|

DMA 0 |

| Free |

DMA 1 |

| Free |

DMA 2 |

| Flexible disk drive controller |

DMA 3 |

| LPT ECP |

DMA 4 |

| DMA controller |

DMA 5 |

| Free |

DMA 6 |

| Free |

DMA 7 |

| Free |

|

|

|

104