N½ Ut•½ M¼p” Kp

7 at• J½p

Memory Controller Hub (8240)

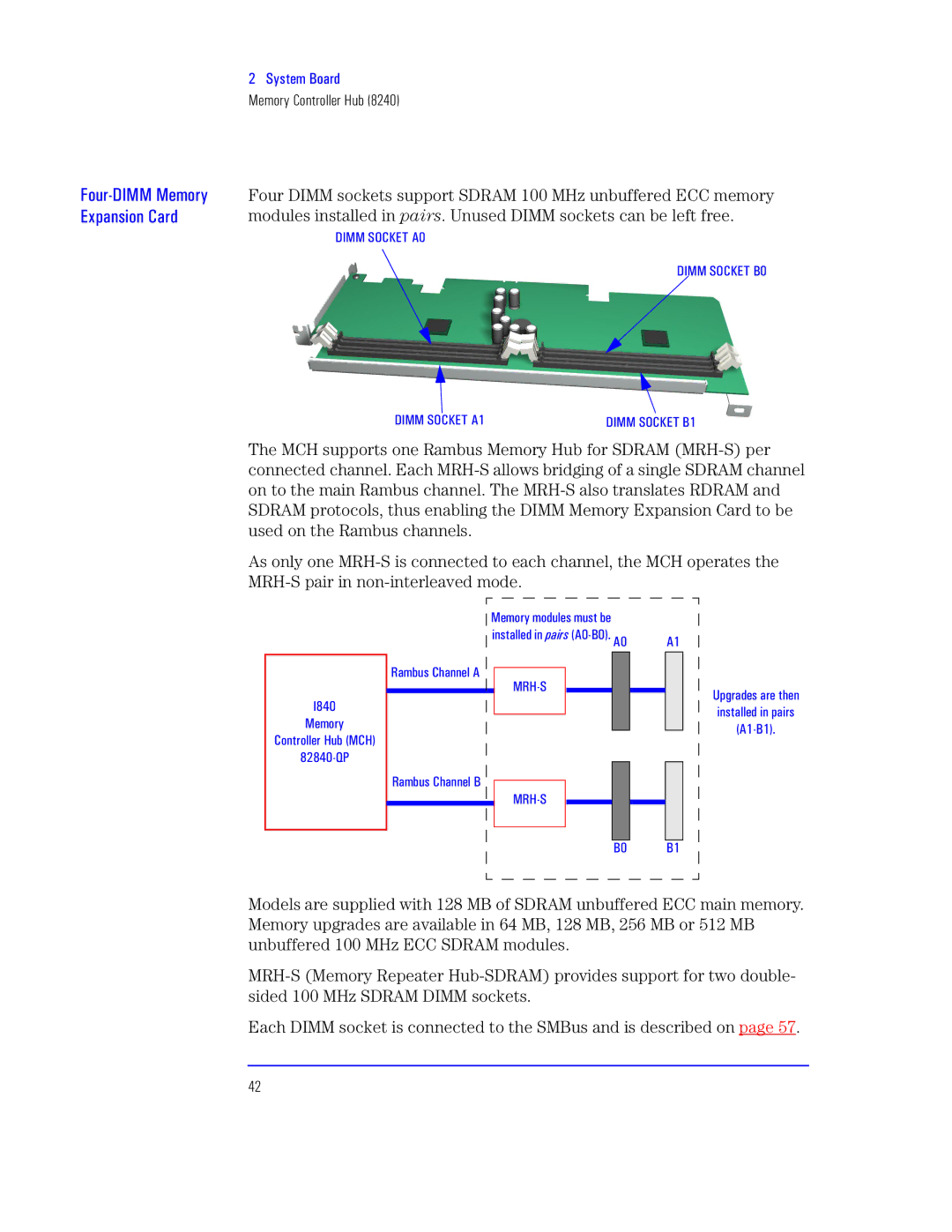

Four DIMM sockets support SDRAM 100 MHz unbuffered ECC memory

modules installed in | . Unused DIMM sockets can be left free. | |

LQUU aWKSMb I5 |

|

|

|

|

|

|

| LQUU aWKSMb J5 |

LQUU aWKSMb I6 |

|

|

| LQUU aWKSMb J6 |

The MCH supports one Rambus Memory Hub for SDRAM

As only one

Q>95

Ut•½

K½”““tq

>7>952YX

|

| Ut•½ •½s“tt |

|

| ||

|

| x”ts x” | ||||

|

| |||||

|

|

|

|

|

|

|

‘p•q Kwp””t“ I |

|

|

|

|

| |

|

|

|

|

| ||

|

|

|

| U‘P2a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

‘p•q Kwp””t“ J

U‘P2a

I6

c¼vst x” x” ¼px

J5 J6

Models are supplied with 128 MB of SDRAM unbuffered ECC main memory. Memory upgrades are available in 64 MB, 128 MB, 256 MB or 512 MB unbuffered 100 MHz ECC SDRAM modules.

Each DIMM socket is connected to the SMBus and is described on page 57.

42