IOX XKQ J

Q•¼“t•t”p½”

c”xp“

IOX

X‘W

K½””tr½

7 a• J½p

Memory Controller Hub (8240)

Pentium III Processor

| IOX 9 J |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| Lt |

|

| |||||

|

|

|

|

|

| Q>95 |

|

| |||||

|

|

| AGP Port |

|

|

|

|

|

| ||||

|

|

|

|

|

|

| Ut•½ |

|

| ||||

|

|

| Interface |

|

|

|

|

|

| ||||

|

|

|

|

|

|

| K½”½““t |

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

| telBtel |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

| gRX33gRX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ez

b½ XKQ <92qx <<

UP

Pq Tx”z 6<2qx

XKQ <92qx << UP

Pq |

gRX33gRX |

![]() Pq Tx”z >2qx

Pq Tx”z >2qx

Q4W K½”½““t

Pq

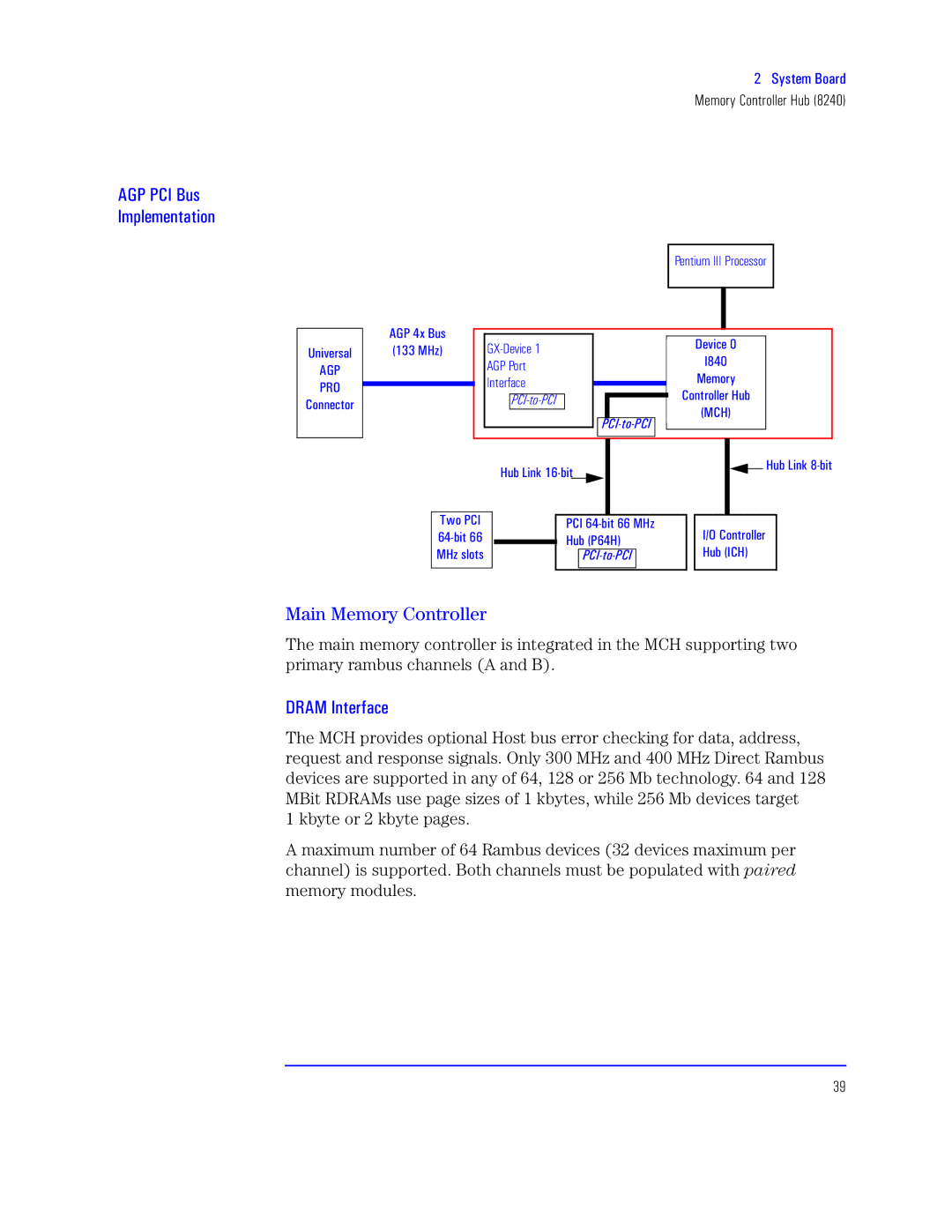

The main memory controller is integrated in the MCH supporting two primary rambus channels (A and B).

L‘IU Q”uprt

The MCH provides optional Host bus error checking for data, address, request and response signals. Only 300 MHz and 400 MHz Direct Rambus devices are supported in any of 64, 128 or 256 Mb technology. 64 and 128 MBit RDRAMs use page sizes of 1 kbytes, while 256 Mb devices target

1 kbyte or 2 kbyte pages.

A maximum number of 64 Rambus devices (32 devices maximum per channel) is supported. Both channels must be populated with memory modules.

39