6 at• Wtt

Internal Features

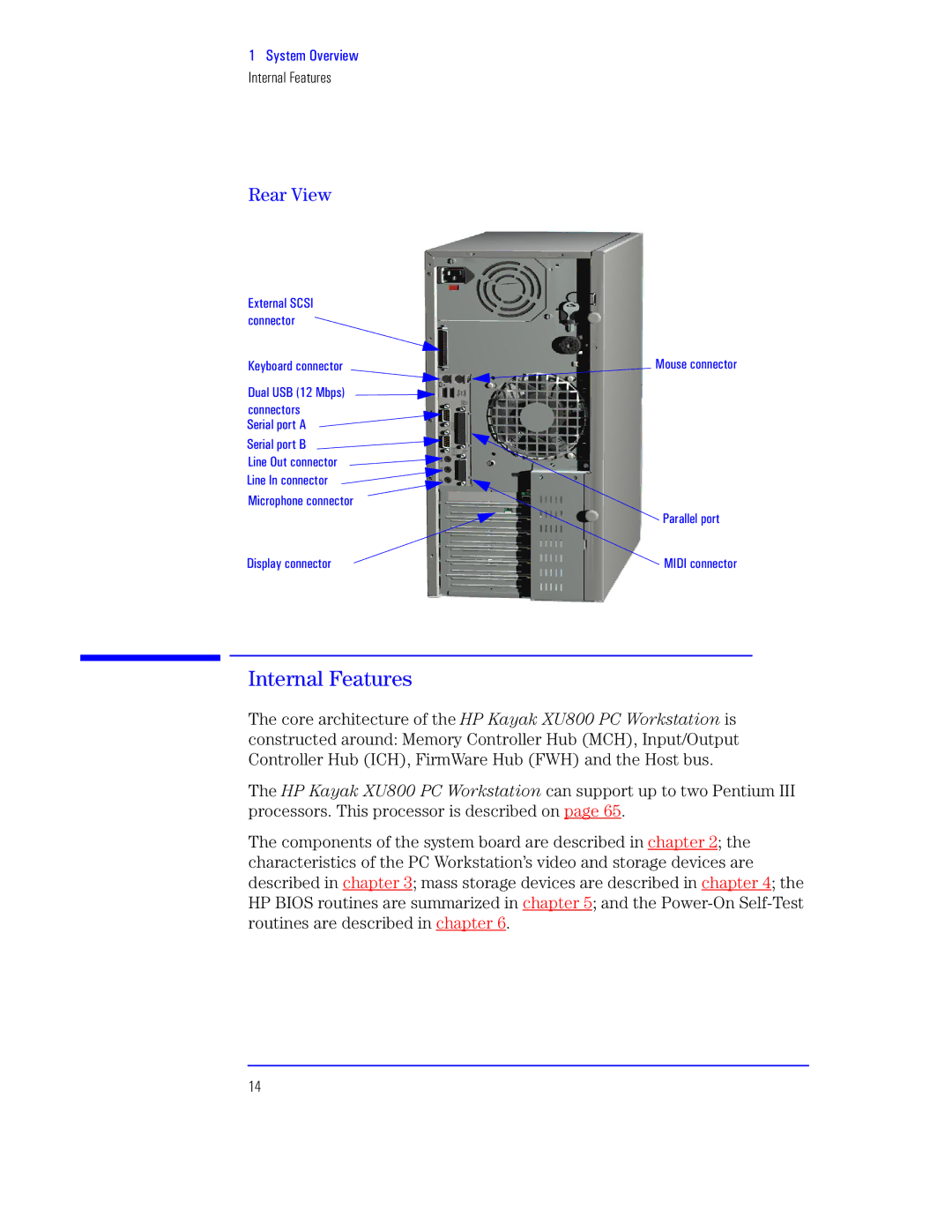

k

Mp“ aKaQ r½””tr

St½p”tr½

Lp“ caJ

atxp“ ¼½ I ![]() atxp“ ¼½ J

atxp“ ¼½ J ![]()

![]() Tx”t W r½””tr

Tx”t W r½””tr ![]()

![]() Tx”t Q” r½””tr½

Tx”t Q” r½””tr½ ![]() Uxr½¼w½”t r½””tr

Uxr½¼w½”t r½””tr

Lx¼“p””tr

U½t r½””tr

Xp““t“ ¼½

UQLQ r½””tr

a V

The core architecture of the Yh c“hT p | is | |

constructed around: Memory Controller Hub (MCH), Input/Output | ||

Controller Hub (ICH), FirmWare Hub (FWH) and the Host bus. |

| |

The Yh c“T p | can support up to two Pentium III | |

processors. This processor is described on page 65.

The components of the system board are described in chapter 2; the characteristics of the PC Workstation’s video and storage devices are described in chapter 3; mass storage devices are described in chapter 4; the HP BIOS routines are summarized in chapter 5; and the

14