7 a• J½p

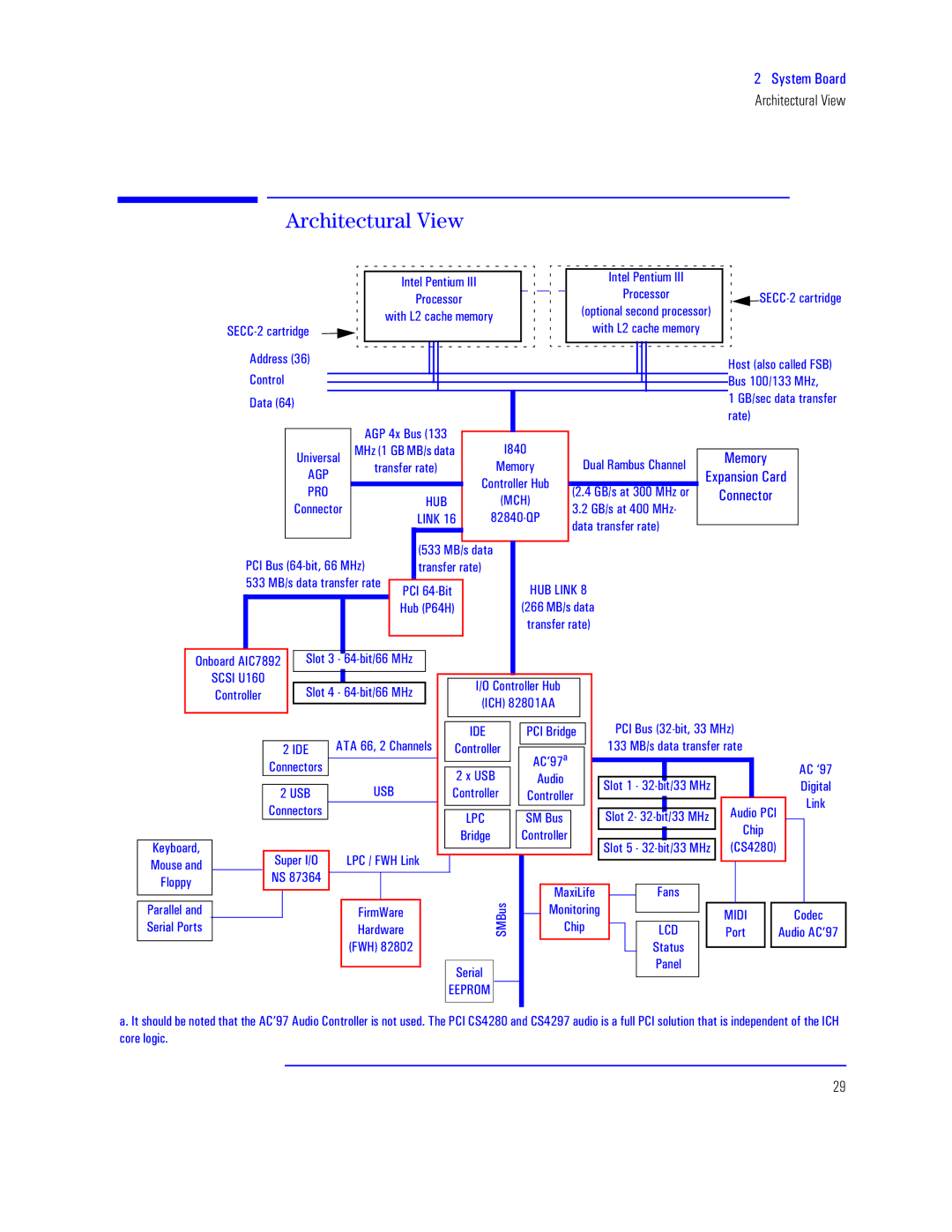

Architectural View

Q®z

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Q”t”• QQQ |

|

|

|

|

|

| |||

|

|

|

|

| Intel Pentium III |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| Xrt |

|

|

|

|

|

| |||||||||

|

|

|

|

|

| Processor |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| aMKK27 rpt | ||||||||||||||

|

|

|

|

| with L2 cache memory |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

aMKK27 rpvt |

|

|

|

|

| x T7 rprwt •t•½ |

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

Isst8<. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| P½ | |||||

K½”½“ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| J554688 UP | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

Lp. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 6 OJ4tr spp p”t | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

| IOX 9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

| Q>95 |

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

| UP OJ UJ4pp |

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

| c”xp“ |

| Lp“ ‘p•q Kwp””t“ |

| Ut•½ |

| ||||||||||||||||||||||

|

|

| ut |

| Ut•½ |

|

| |||||||||||||||||||||

| IOX |

|

|

| M¼p”½” Kp |

| ||||||||||||||||||||||

|

|

|

|

|

|

|

|

| K½”““tq |

|

|

|

|

| ||||||||||||||

| X‘W |

|

|

|

|

|

|

|

| (2.4 GB/s at 300 MHz or | K½””tr½ |

| ||||||||||||||||

|

|

|

| PcJ |

|

| ||||||||||||||||||||||

| K½””tr½ |

|

|

|

| 3.2 GB/s at 400 MHz- |

|

|

|

|

|

| ||||||||||||||||

|

|

|

| TQVS 6< |

| >7>952YX |

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

| data transfer rate) |

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| XKQ J |

|

|

|

| ||||

| ut |

|

|

|

|

| |||

| :88 UJ4p p”t t |

| XKQ <92Jx |

| PcJ TQVS > |

|

|

| |

|

|

|

|

|

|

|

| ||

|

|

|

| P |

|

|

|

| |

|

|

|

|

|

| . |

|

|

|

| W”q½ps IQK=>A7 | a“½ 8 2 <92qx4<< UP |

|

|

|

|

| ||

| aKaQ c6<5 | a“½ 9 2 <92qx4<< UP | I/OQ4W ControllerK½”½““t PqHub |

|

|

| |||

| K½”““t |

|

|

| |||||

|

|

|

| ||||||

|

|

|

|

|

|

|

| ||

|

|

| IbI <<1 7 Kwp””t“ | IDE | PCI Bridge | XKQ J872qx1 88 UP |

|

| |

|

| 7 QLM | Controller | AC’97p | 688 UJ4spp p”ut t |

|

| ||

| K½””tr½ |

|

| 7 caJ |

|

| AC ‘97 | ||

|

|

| Audio | a“½ 6 2 872qx488 UP |

| ||||

|

|

|

| caJ |

| Digital | |||

|

| 7 caJ |

| K½”““t | Controller |

| |||

|

|

|

|

| Link | ||||

| K½””tr½ |

|

| LPC | aU J | a“½ 72 872qx488 UP | Ix½ XKQ | ||

|

|

|

| ||||||

|

|

|

|

| Bridge | K½”½““t |

| Kwx¼ |

|

St½p1 |

|

|

|

| a“½ : 2 872qx488 UP |

| |||

a¼t4W |

| TXK 4 NeP Tx”z |

|

|

| ||||

U½ p”s |

|

|

|

|

|

| |||

Va >=8<9 |

|

|

|

|

|

|

| ||

N“½¼¼ |

|

|

| Up | Np” |

|

| ||

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| ||

Xp““t“ p”s |

|

|

| Nxep | aUJ | U½”xx”v |

| MIDI | K½str |

at“ X½ |

|

|

| Pppt | Kwx¼ | TKL | Port | Audio AC‘97 | |

|

|

|

|

|

| a |

|

| |

|

|

|

|

| at“ |

| Xp”t“ |

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

| MMX‘WU |

|

|

|

|

a. It should be noted that the AC’97 Audio Controller is not used. The PCI CS4280 and CS4297 audio is a full PCI solution that is independent of the ICH core logic.

29