7 a• J½p

PCI 64-bit Hub

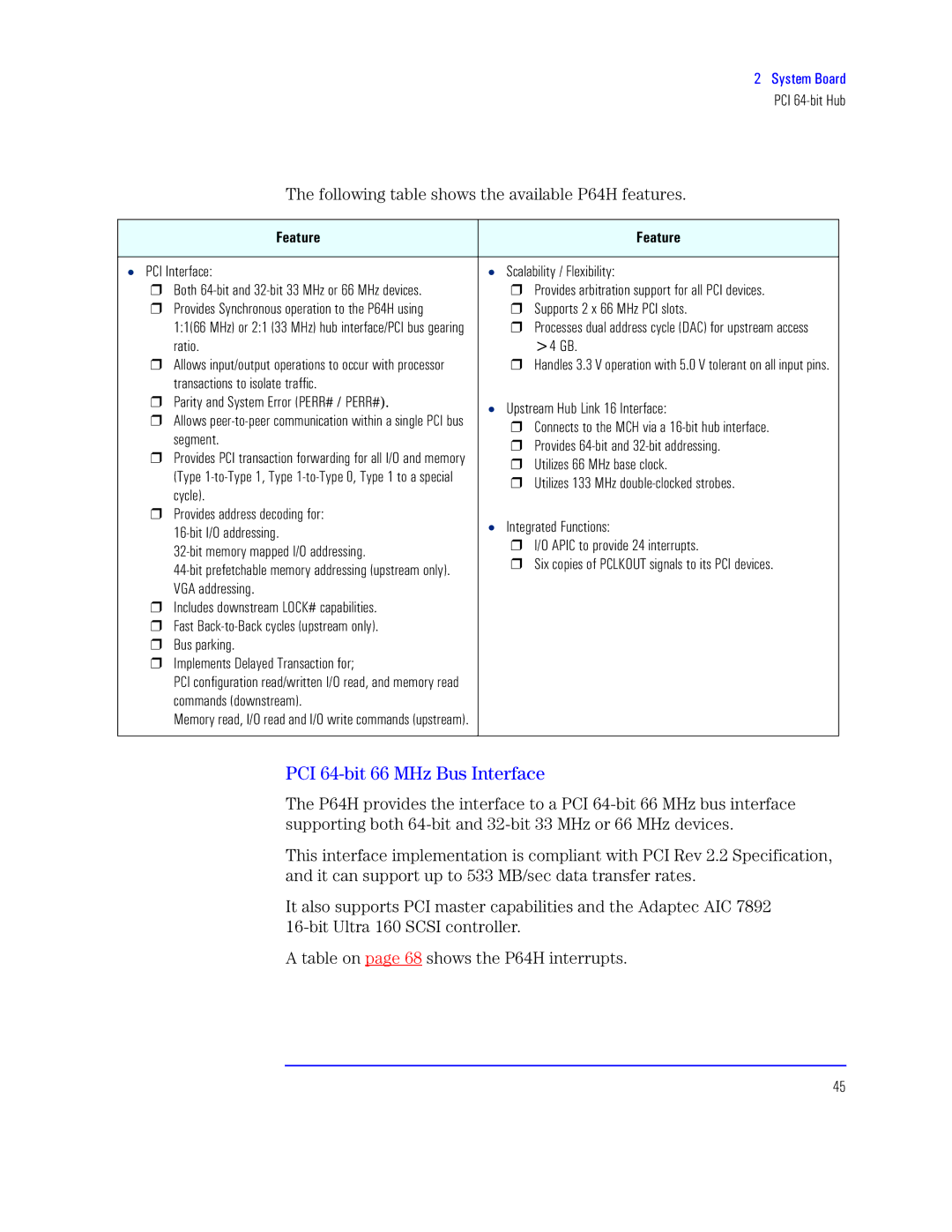

The following table shows the available P64H features.

Otp |

| Otpt | |

|

|

| |

• PCI Interface: | • | Scalability / Flexibility: | |

❒ Both |

| ❒ Provides arbitration support for all PCI devices. | |

❒ Provides Synchronous operation to the P64H using |

| ❒ Supports 2 x 66 MHz PCI slots. | |

1:1(66 MHz) or 2:1 (33 MHz) hub interface/PCI bus gearing |

| ❒ Processes dual address cycle (DAC) for upstream access | |

ratio. |

| >4 GB. | |

❒ Allows input/output operations to occur with processor |

| ❒ Handles 3.3 V operation with 5.0 V tolerant on all input pins. | |

transactions to isolate traffic. |

|

| |

❒ Parity and System Error (PERR# / PERR#). | • | Upstream Hub Link 16 Interface: | |

❒ Allows | |||

| ❒ Connects to the MCH via a | ||

segment. |

| ||

| ❒ Provides | ||

❒ Provides PCI transaction forwarding for all I/O and memory |

| ||

| ❒ Utilizes 66 MHz base clock. | ||

(Type |

| ||

| ❒ Utilizes 133 MHz | ||

cycle). |

| ||

|

| ||

❒ Provides address decoding for: | • | Integrated Functions: | |

| ❒ I/O APIC to provide 24 interrupts. | ||

| |||

| ❒ Six copies of PCLKOUT signals to its PCI devices. | ||

| |||

|

| ||

VGA addressing. |

|

|

❒Includes downstream LOCK# capabilities.

❒Fast

❒Bus parking.

❒Implements Delayed Transaction for;

PCI configuration read/written I/O read, and memory read commands (downstream).

Memory read, I/O read and I/O write commands (upstream).

hSa EC6™ a

The P64H provides the interface to a PCI

This interface implementation is compliant with PCI Rev 2.2 Specification, and it can support up to 533 MB/sec data transfer rates.

It also supports PCI master capabilities and the Adaptec AIC 7892

A table on page 68 shows the P64H interrupts.

45