< btUt

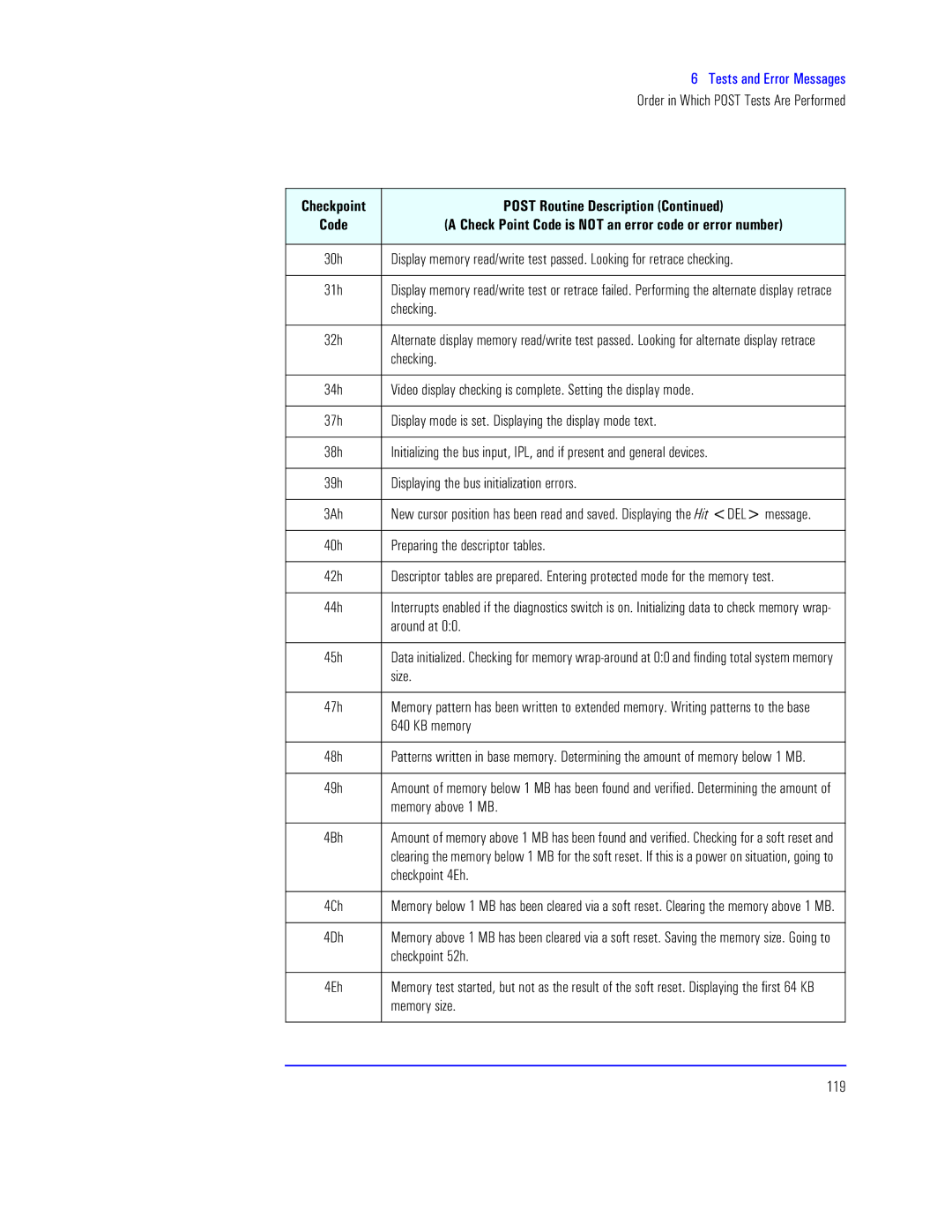

Order in Which POST Tests Are Performed

Lwtrz | ZYab ]xt |

L | |

|

|

30h | Display memory read/write test passed. Looking for retrace checking. |

|

|

31h | Display memory read/write test or retrace failed. Performing the alternate display retrace |

| checking. |

|

|

32h | Alternate display memory read/write test passed. Looking for alternate display retrace |

| checking. |

|

|

34h | Video display checking is complete. Setting the display mode. |

|

|

37h | Display mode is set. Displaying the display mode text. |

|

|

38h | Initializing the bus input, IPL, and if present and general devices. |

|

|

39h | Displaying the bus initialization errors. |

|

|

3Ah | New cursor position has been read and saved. Displaying the k <DEL> message. |

|

|

40h | Preparing the descriptor tables. |

|

|

42h | Descriptor tables are prepared. Entering protected mode for the memory test. |

|

|

44h | Interrupts enabled if the diagnostics switch is on. Initializing data to check memory wrap- |

| around at 0:0. |

|

|

45h | Data initialized. Checking for memory |

| size. |

|

|

47h | Memory pattern has been written to extended memory. Writing patterns to the base |

| 640 KB memory |

|

|

48h | Patterns written in base memory. Determining the amount of memory below 1 MB. |

|

|

49h | Amount of memory below 1 MB has been found and verified. Determining the amount of |

| memory above 1 MB. |

|

|

4Bh | Amount of memory above 1 MB has been found and verified. Checking for a soft reset and |

| clearing the memory below 1 MB for the soft reset. If this is a power on situation, going to |

| checkpoint 4Eh. |

|

|

4Ch | Memory below 1 MB has been cleared via a soft reset. Clearing the memory above 1 MB. |

|

|

4Dh | Memory above 1 MB has been cleared via a soft reset. Saving the memory size. Going to |

| checkpoint 52h. |

|

|

4Eh | Memory test started, but not as the result of the soft reset. Displaying the first 64 KB |

| memory size. |

|

|