7 a• J½p

Memory Controller Hub (8240)

Otp |

| Otpt |

|

|

|

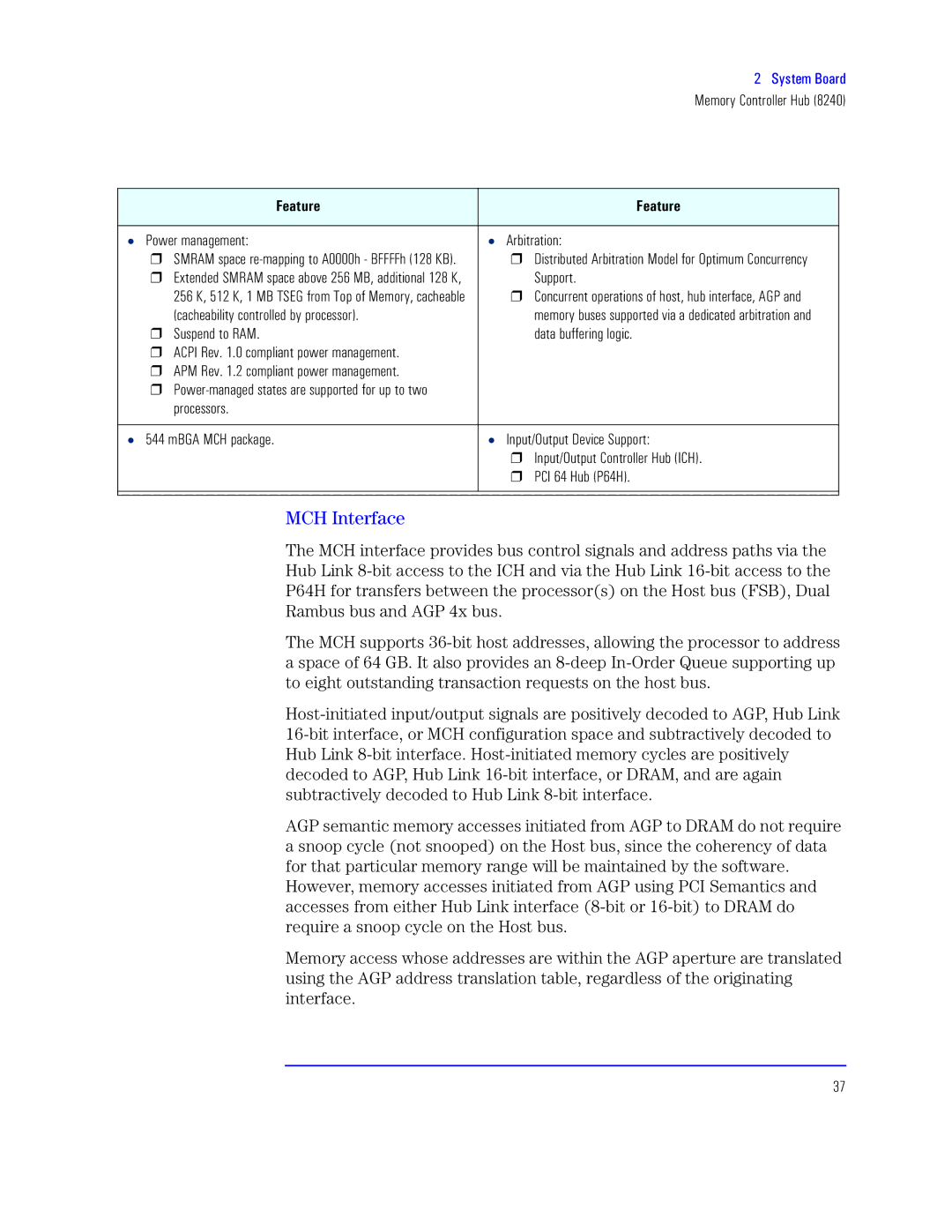

• Power management: | • | Arbitration: |

❒ SMRAM space |

| ❒ Distributed Arbitration Model for Optimum Concurrency |

❒ Extended SMRAM space above 256 MB, additional 128 K, |

| Support. |

256 K, 512 K, 1 MB TSEG from Top of Memory, cacheable |

| ❒ Concurrent operations of host, hub interface, AGP and |

(cacheability controlled by processor). |

| memory buses supported via a dedicated arbitration and |

❒ Suspend to RAM. |

| data buffering logic. |

❒ ACPI Rev. 1.0 compliant power management. |

|

|

❒ APM Rev. 1.2 compliant power management. |

|

|

❒ |

|

|

processors. |

|

|

|

|

|

• 544 mBGA MCH package. | • | Input/Output Device Support: |

|

| ❒ Input/Output Controller Hub (ICH). |

|

| ❒ PCI 64 Hub (P64H). |

|

|

|

|

|

|

eSX a

The MCH interface provides bus control signals and address paths via the

Hub Link

P64H for transfers between the processor(s) on the Host bus (FSB), Dual

Rambus bus and AGP 4x bus.

The MCH supports

AGP semantic memory accesses initiated from AGP to DRAM do not require a snoop cycle (not snooped) on the Host bus, since the coherency of data for that particular memory range will be maintained by the software. However, memory accesses initiated from AGP using PCI Semantics and accesses from either Hub Link interface

Memory access whose addresses are within the AGP aperture are translated using the AGP address translation table, regardless of the originating interface.

37