7 a• J½p

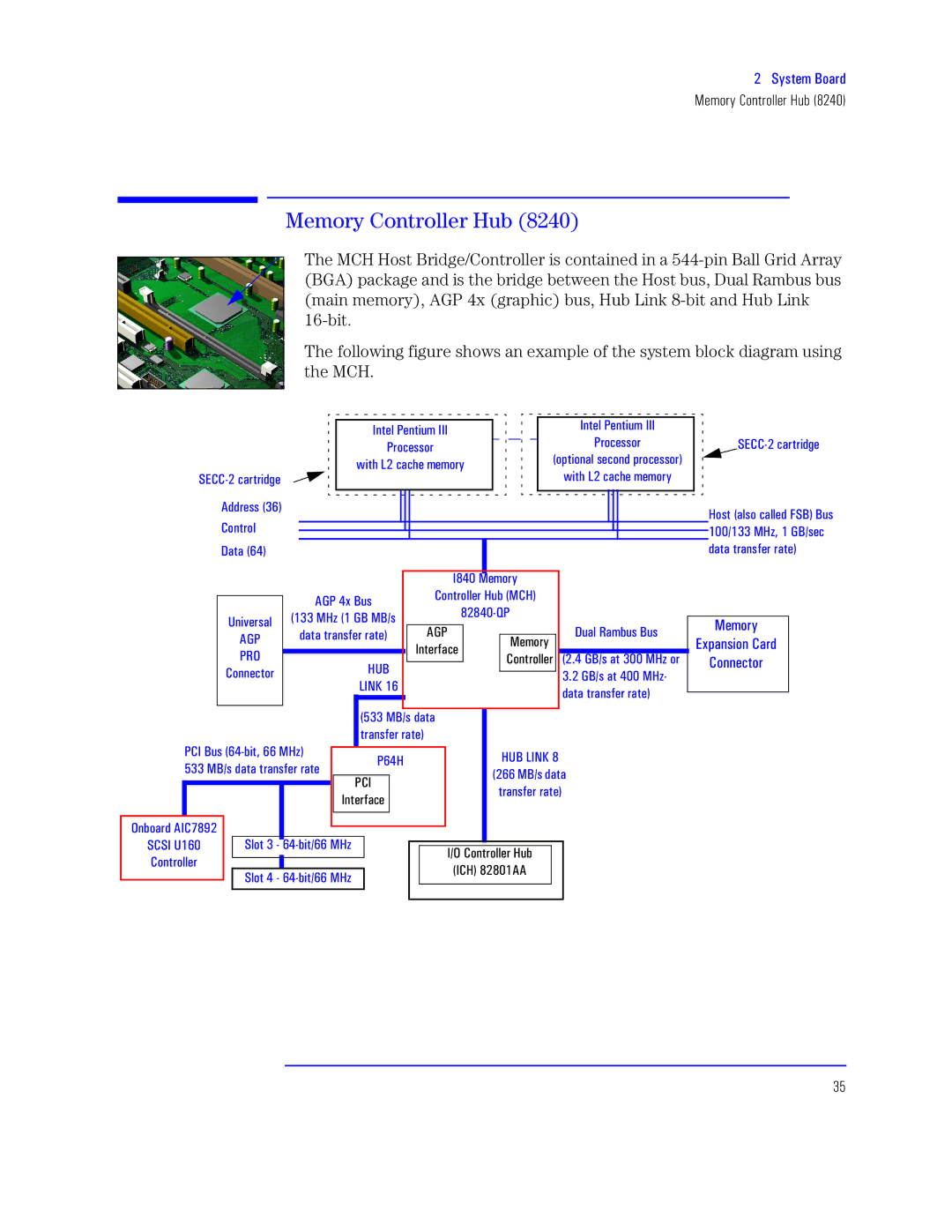

Memory Controller Hub (8240)

e SGAC92

The MCH Host Bridge/Controller is contained in a

The following figure shows an example of the system block diagram using the MCH.

|

| Q”t“ Xt”x• QQQ |

| Q”t”• QQQ | |

|

|

| Xrt | ||

|

| X½rt½ |

|

| |

|

|

| |||

|

| x rprwt •t•½ |

| ||

aMKK27 rpvt |

|

| x T7 rprwt •t•½ | ||

|

|

| |||

| Isst8<. |

|

|

|

|

| K½”½“ |

|

|

|

|

| Lp. |

|

|

|

|

|

|

|

| Q>95 Ut•½ |

|

|

| IOX 9 J | K½”““t Pq |

| |

|

|

| >7>952YX |

| |

| c”x“ |

|

| ||

| IOX |

| Lp“ ‘p•q J | ||

| IOX | sp p”ut p. | Ut•½ | ||

|

|

| |||

| X‘W | Q”tuprt | K½”““t | ||

| PcJ |

| |||

| K½””tr |

|

| 837 OJ4p 955 UP | |

| TQVS 6< |

|

| ||

|

|

|

| sp ut t. | |

|

|

|

|

| |

|

|

|

|

| |

|

| . |

|

|

|

XKQ J<92qx1 << UP | X<9P |

| PcJ TQVS > |

| |

:88 UJ4p p”t t |

|

| |||

XKQ |

|

| |||

|

|

|

| ||

|

|

| t. |

| |

|

| Q”tprt |

|

| |

|

|

|

|

| |

W”q½p IQK=>A7 | a“½ 8 2 <92qx4<< UP |

|

|

| |

aKaQ c6<5 | Q4W K½”½““t Pq |

| |||

K½”““t |

|

|

| ||

a“½ 9 2 <92qx4<< UP |

|

| |||

|

|

| |||

|

|

|

| ||

aMKK27 rpsvt

P½

Ut•½

M¼p”

K½””tr½

35