< btUt

Order in Which POST Tests Are Performed

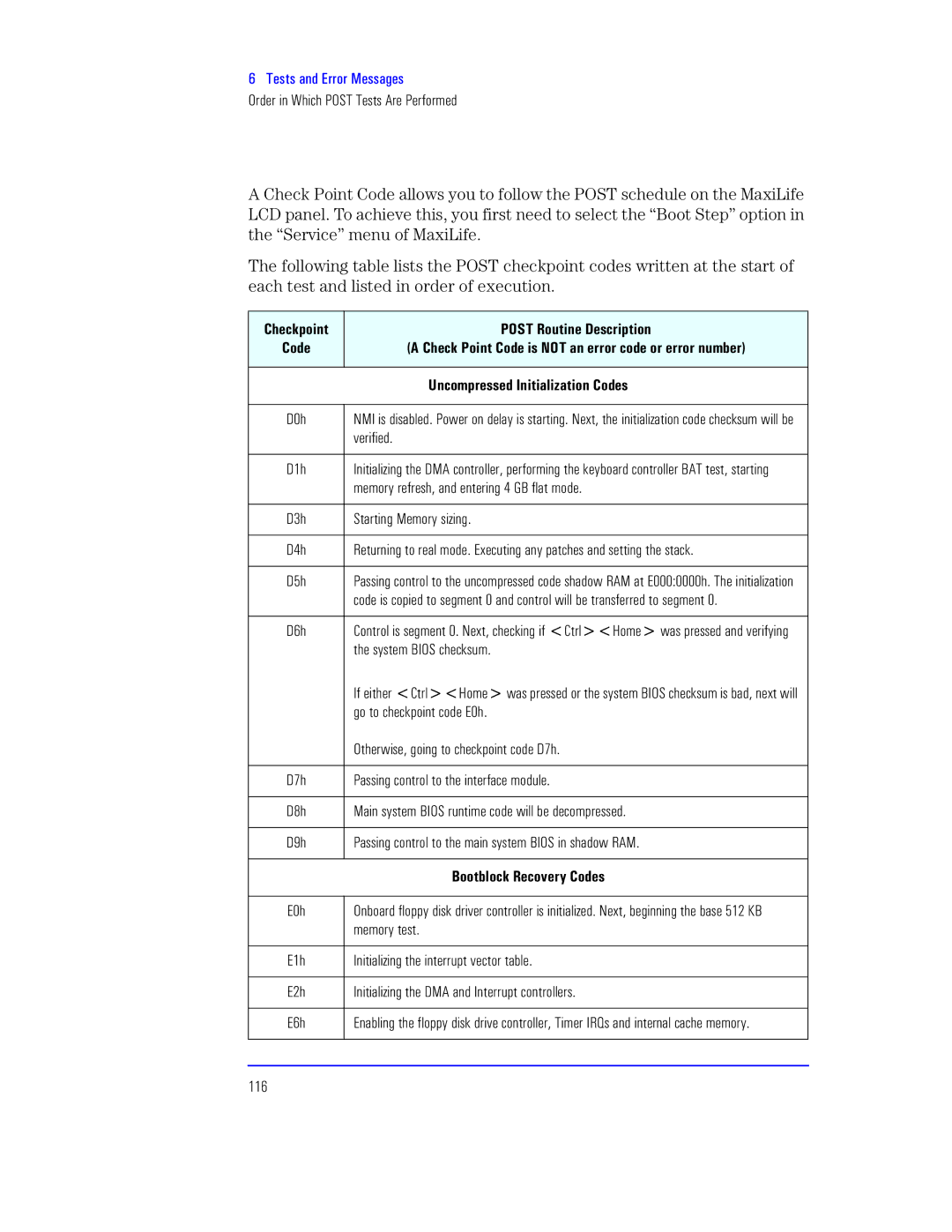

A Check Point Code allows you to follow the POST schedule on the MaxiLife LCD panel. To achieve this, you first need to select the “Boot Step” option in the “Service” menu of MaxiLife.

The following table lists the POST checkpoint codes written at the start of each test and listed in order of execution.

Lwtrz

L

ZYab ]xt Mtr

-J Lwtrz Z x WYb p qt.

crtx L

D0h | NMI is disabled. Power on delay is starting. Next, the initialization code checksum will be |

| verified. |

|

|

D1h | Initializing the DMA controller, performing the keyboard controller BAT test, starting |

| memory refresh, and entering 4 GB flat mode. |

|

|

D3h | Starting Memory sizing. |

|

|

D4h | Returning to real mode. Executing any patches and setting the stack. |

|

|

D5h | Passing control to the uncompressed code shadow RAM at E000:0000h. The initialization |

| code is copied to segment 0 and control will be transferred to segment 0. |

|

|

D6h | Control is segment 0. Next, checking if <Ctrl><Home> was pressed and verifying |

| the system BIOS checksum. |

| If either <Ctrl><Home> was pressed or the system BIOS checksum is bad, next will |

| go to checkpoint code E0h. |

| Otherwise, going to checkpoint code D7h. |

|

|

D7h | Passing control to the interface module. |

|

|

D8h | Main system BIOS runtime code will be decompressed. |

|

|

D9h | Passing control to the main system BIOS in shadow RAM. |

|

|

| Krz ]tr |

|

|

E0h | Onboard floppy disk driver controller is initialized. Next, beginning the base 512 KB |

| memory test. |

|

|

E1h | Initializing the interrupt vector table. |

|

|

E2h | Initializing the DMA and Interrupt controllers. |

|

|

E6h | Enabling the floppy disk drive controller, Timer IRQs and internal cache memory. |

|

|

|

|

116