MultiProcessor Specification

4GB

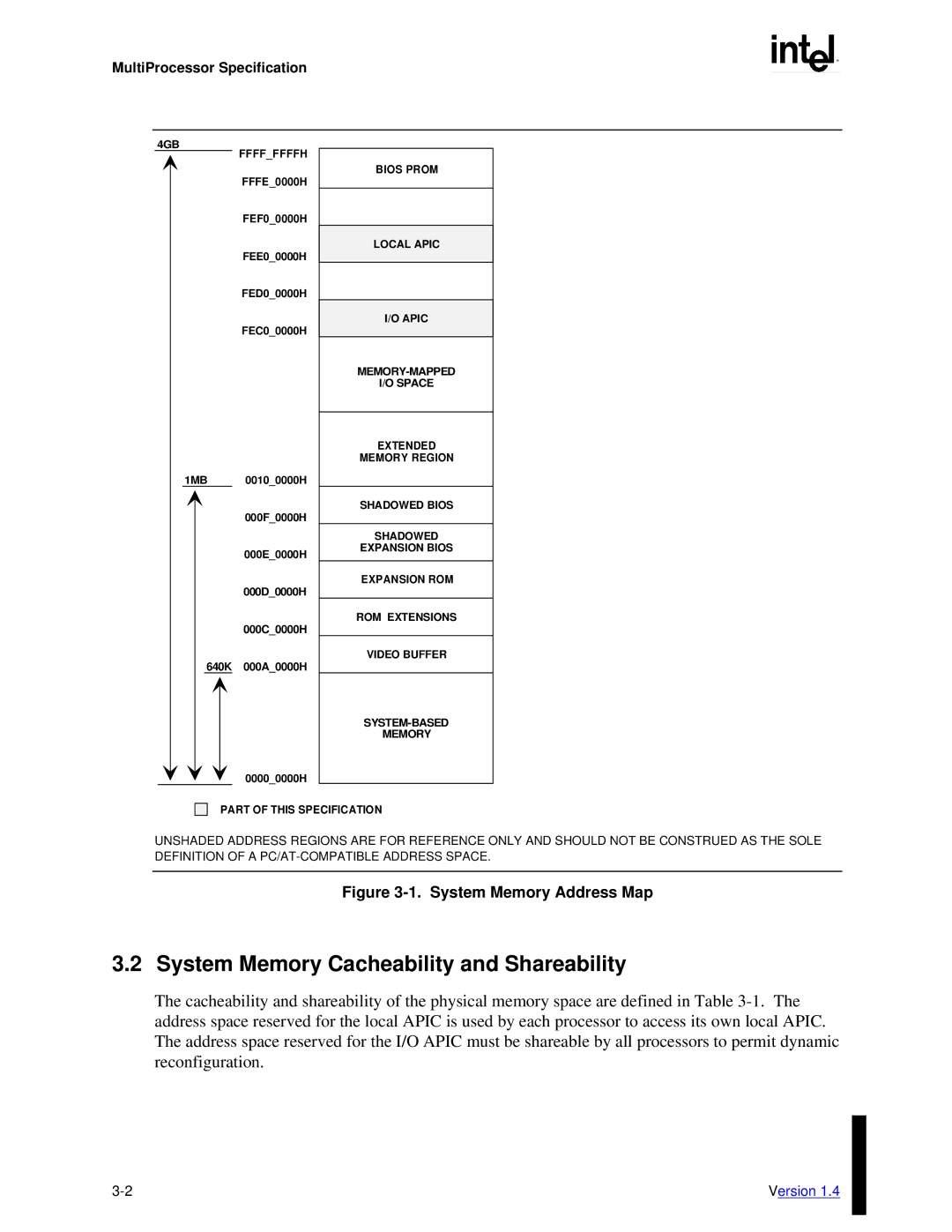

FFFF_FFFFH

FFFE_0000H

FEF0_0000H

FEE0_0000H

FED0_0000H

FEC0_0000H

1MB 0010_0000H

000F_0000H

000E_0000H

000D_0000H

000C_0000H

640K 000A_0000H

0000_0000H

BIOS PROM

LOCAL APIC

I/O APIC

I/O SPACE

EXTENDED

MEMORY REGION

SHADOWED BIOS

SHADOWED

EXPANSION BIOS

EXPANSION ROM

ROM EXTENSIONS

VIDEO BUFFER

MEMORY

PART OF THIS SPECIFICATION

UNSHADED ADDRESS REGIONS ARE FOR REFERENCE ONLY AND SHOULD NOT BE CONSTRUED AS THE SOLE DEFINITION OF A

Figure 3-1. System Memory Address Map

3.2 System Memory Cacheability and Shareability

The cacheability and shareability of the physical memory space are defined in Table

Version 1.4 |