MultiProcessor Specification

31 | 28 27 | 24 23 | 20 19 | 16 15 | 12 11 | 8 |

| 7 | 4 | 3 | 0 |

| ||||

|

|

|

|

|

| RESERVED |

|

|

|

|

| PARENT BUS |

| 04H | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

| BUS INFO | S |

| BUS ID |

| ENTRY LENGTH |

| ENTRY TYPE |

| 00H | |||||

|

|

|

|

|

|

|

| 129 |

| |||||||

|

|

|

|

|

| |||||||||||

|

| RESERVED |

|

|

|

|

|

|

|

| ||||||

|

| D |

|

|

|

|

|

|

|

|

|

|

|

| ||

31 | 28 27 | 24 23 | 20 19 | 16 15 | 12 11 | 8 |

| 7 | 4 | 3 | 0 |

| ||||

|

|

|

|

|

| |||||||||||

|

|

| Figure |

|

| |||||||||||

| Table |

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

| Offset | Length |

|

|

|

|

|

|

|

| ||||

| Field | (in bytes:bits) (in bits) | Description |

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

| ||||||||

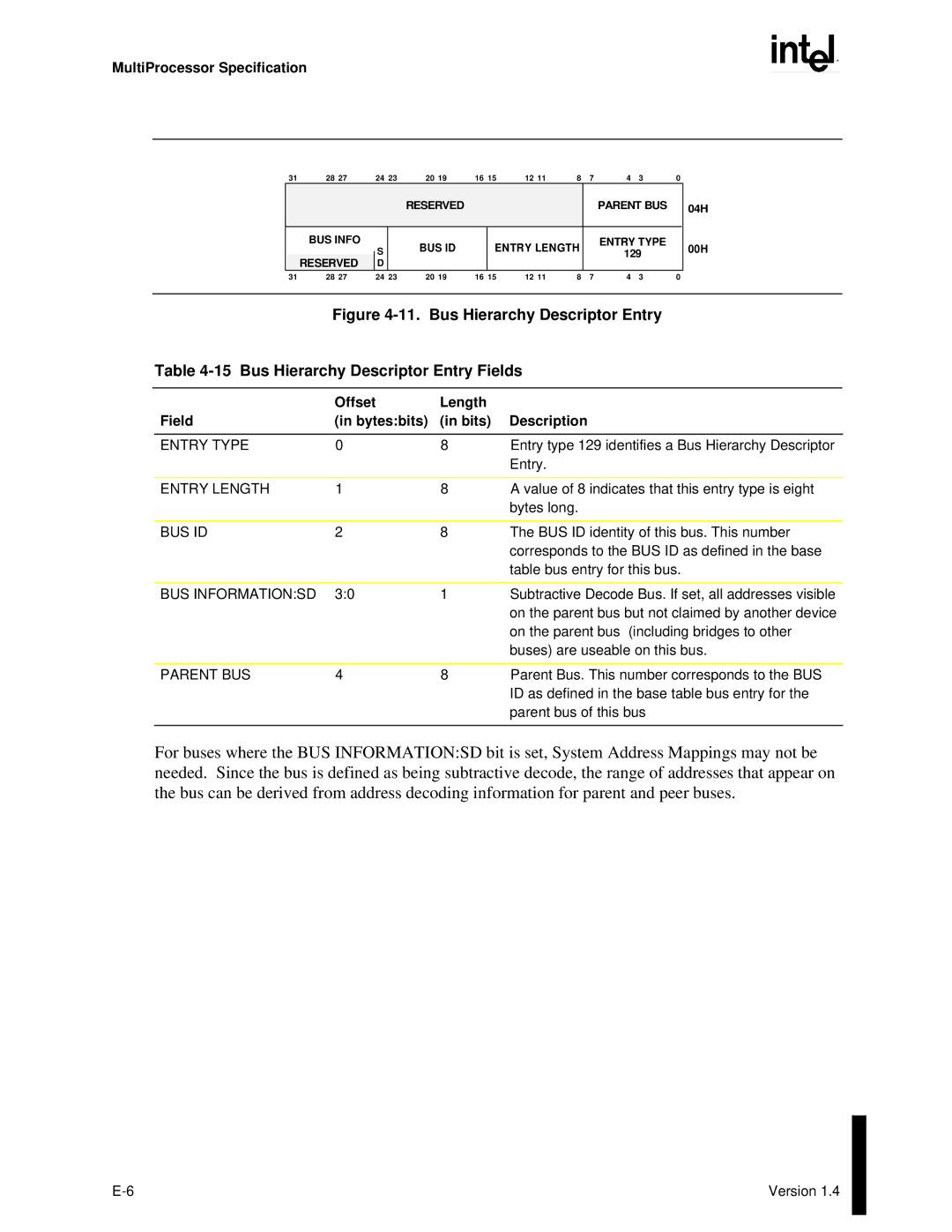

| ENTRY TYPE | 0 |

|

| 8 |

|

| Entry type 129 identifies a Bus Hierarchy Descriptor | ||||||||

|

|

|

|

|

|

|

|

| Entry. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

| ENTRY LENGTH | 1 |

|

| 8 |

|

| A value of 8 indicates that this entry type is eight | ||||||||

|

|

|

|

|

|

|

|

| bytes long. |

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| ||||||||

| BUS ID | 2 |

|

| 8 |

|

| The BUS ID identity of this bus. This number | ||||||||

|

|

|

|

|

|

|

|

| corresponds to the BUS ID as defined in the base | |||||||

|

|

|

|

|

|

|

|

| table bus entry for this bus. | |||||||

|

|

|

|

|

|

|

|

| ||||||||

| BUS INFORMATION:SD | 3:0 |

|

| 1 |

|

| Subtractive Decode Bus. If set, all addresses visible | ||||||||

|

|

|

|

|

|

|

|

| on the parent bus but not claimed by another device | |||||||

|

|

|

|

|

|

|

|

| on the parent bus | (including bridges to other | ||||||

|

|

|

|

|

|

|

|

| buses) are useable on this bus. | |||||||

|

|

|

|

|

|

|

|

| ||||||||

| PARENT BUS | 4 |

|

| 8 |

|

| Parent Bus. This number corresponds to the BUS | ||||||||

|

|

|

|

|

|

|

|

| ID as defined in the base table bus entry for the | |||||||

|

|

|

|

|

|

|

|

| parent bus of this bus |

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

For buses where the BUS INFORMATION:SD bit is set, System Address Mappings may not be needed. Since the bus is defined as being subtractive decode, the range of addresses that appear on the bus can be derived from address decoding information for parent and peer buses.

Version 1.4 |