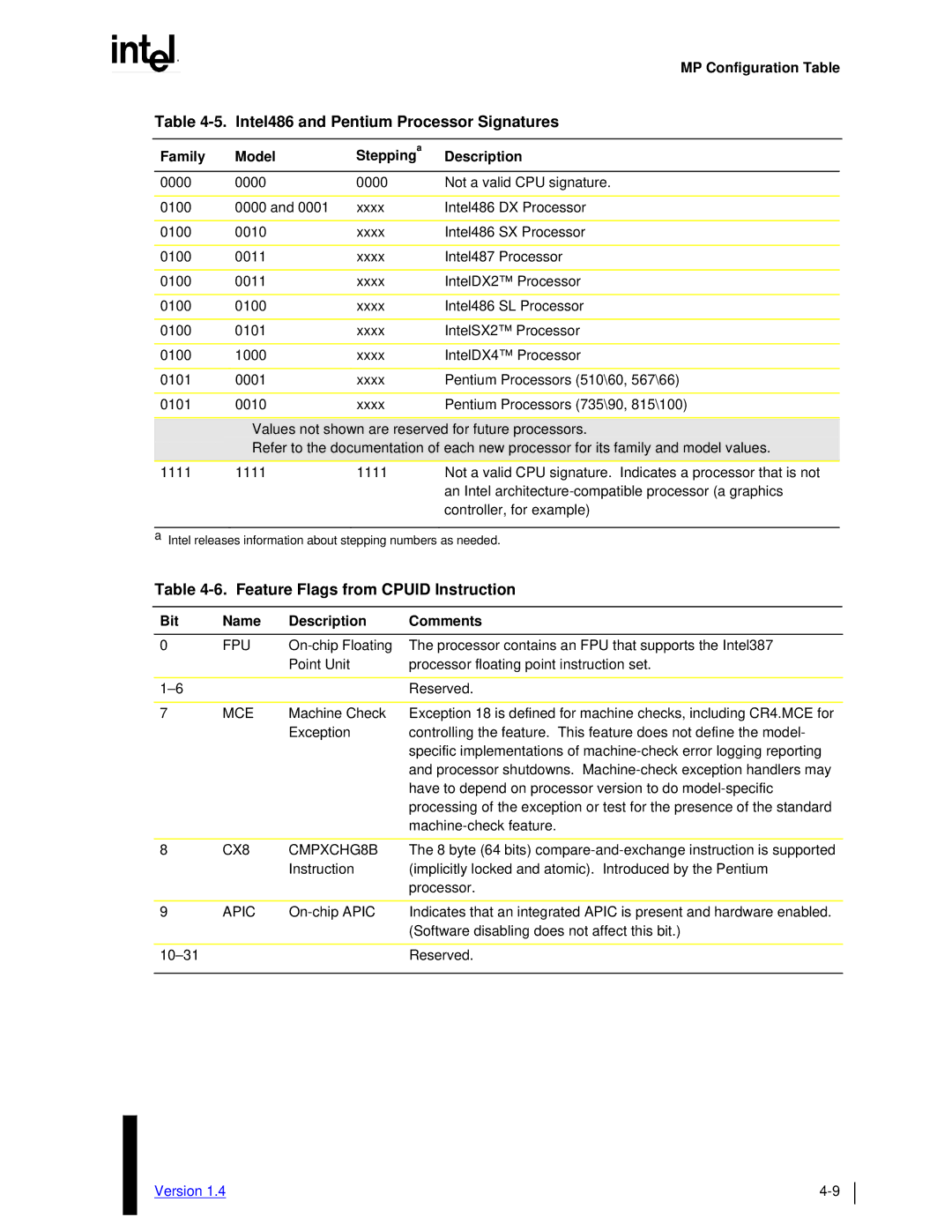

MP Configuration Table

Table 4-5. Intel486 and Pentium Processor Signatures

Family | Model | Steppinga | Description |

|

|

|

|

0000 | 0000 | 0000 | Not a valid CPU signature. |

|

|

|

|

0100 | 0000 and 0001 | xxxx | Intel486 DX Processor |

|

|

|

|

0100 | 0010 | xxxx | Intel486 SX Processor |

|

|

|

|

0100 | 0011 | xxxx | Intel487 Processor |

|

|

|

|

0100 | 0011 | xxxx | IntelDX2™ Processor |

|

|

|

|

0100 | 0100 | xxxx | Intel486 SL Processor |

|

|

|

|

0100 | 0101 | xxxx | IntelSX2™ Processor |

|

|

|

|

0100 | 1000 | xxxx | IntelDX4™ Processor |

|

|

|

|

0101 | 0001 | xxxx | Pentium Processors (510\60, 567\66) |

|

|

|

|

0101 | 0010 | xxxx | Pentium Processors (735\90, 815\100) |

|

| ||

| Values not shown are reserved for future processors. | ||

| Refer to the documentation of each new processor for its family and model values. | ||

|

|

|

|

1111 | 1111 | 1111 | Not a valid CPU signature. Indicates a processor that is not |

|

|

| an Intel |

|

|

| controller, for example) |

a Intel releases information about stepping numbers as needed.

Table 4-6. Feature Flags from CPUID Instruction

Bit | Name | Description | Comments |

0 | FPU | The processor contains an FPU that supports the Intel387 | |

|

| Point Unit | processor floating point instruction set. |

|

|

|

|

|

| Reserved. | |

|

|

|

|

7 | MCE | Machine Check | Exception 18 is defined for machine checks, including CR4.MCE for |

|

| Exception | controlling the feature. This feature does not define the model- |

|

|

| specific implementations of |

|

|

| and processor shutdowns. |

|

|

| have to depend on processor version to do |

|

|

| processing of the exception or test for the presence of the standard |

|

|

| |

|

|

|

|

8 | CX8 | CMPXCHG8B | The 8 byte (64 bits) |

|

| Instruction | (implicitly locked and atomic). Introduced by the Pentium |

|

|

| processor. |

|

|

|

|

9 | APIC | Indicates that an integrated APIC is present and hardware enabled. | |

|

|

| (Software disabling does not affect this bit.) |

|

|

|

|

|

| Reserved. | |

|

|

|

|

Version 1.4 |