MultiProcessor Specification

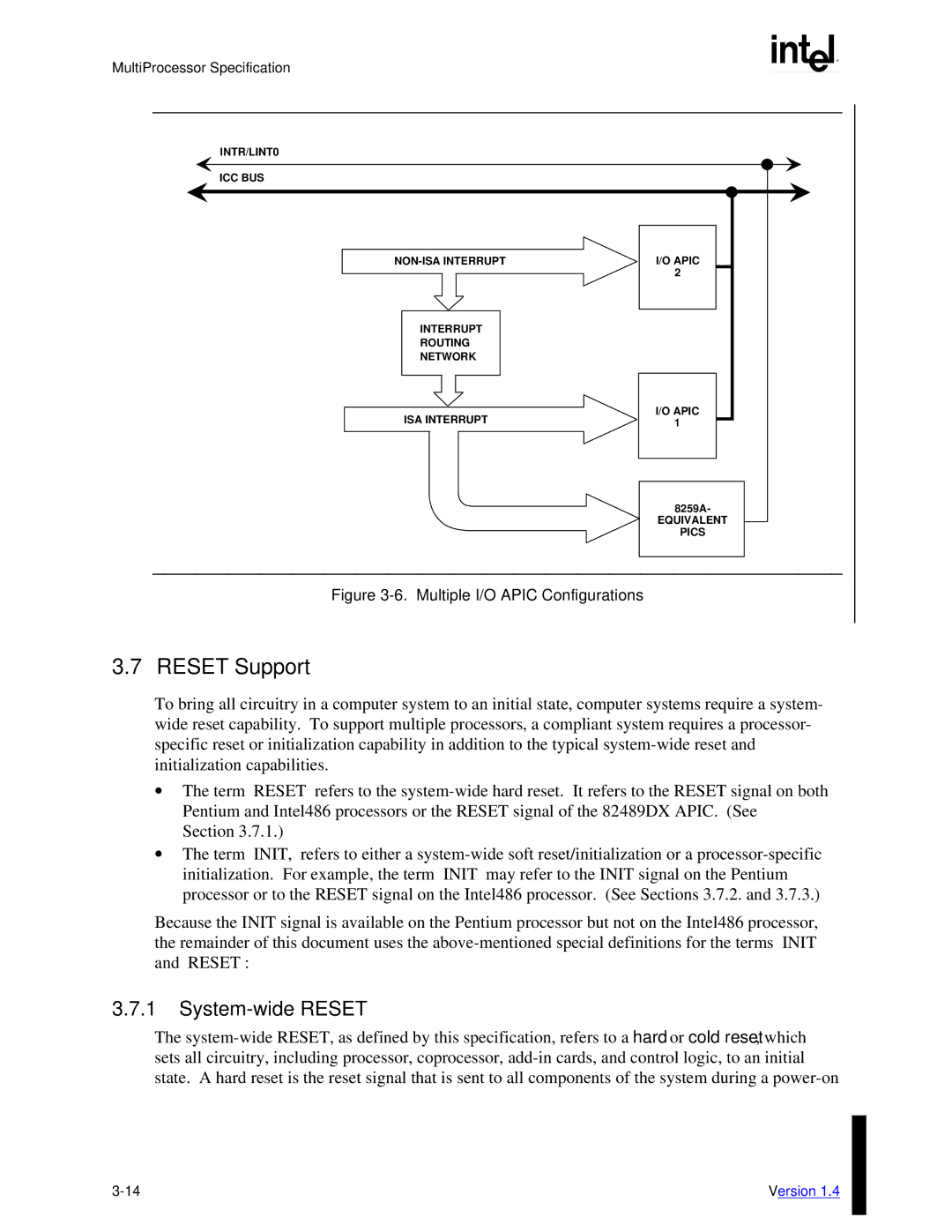

INTR/LINT0

ICC BUS

INTERRUPT

ROUTING

NETWORK

I/O APIC

2

ISA INTERRUPT

I/O APIC

1

8259A-

EQUIVALENT

PICS

Figure 3-6. Multiple I/O APIC Configurations

3.7 RESET Support

To bring all circuitry in a computer system to an initial state, computer systems require a system- wide reset capability. To support multiple processors, a compliant system requires a processor- specific reset or initialization capability in addition to the typical

∙The term “RESET” refers to the

∙The term “INIT,” refers to either a

Because the INIT signal is available on the Pentium processor but not on the Intel486 processor, the remainder of this document uses the

3.7.1System-wide RESET

The

Version 1.4 |