MP Configuration Table

information byte 2, the IMCR present bit, is used by the operating system to determine whether PIC Mode or Virtual Wire Mode is implemented by the system.

The physical address pointer field contains the address of the beginning of the MP configuration table. If it is nonzero, the MP configuration table can be accessed at the physical address provided in the pointer structure. This field must be all zeros if the MP configuration table does not exist.

4.4.1 System Address Space Mapping Entries

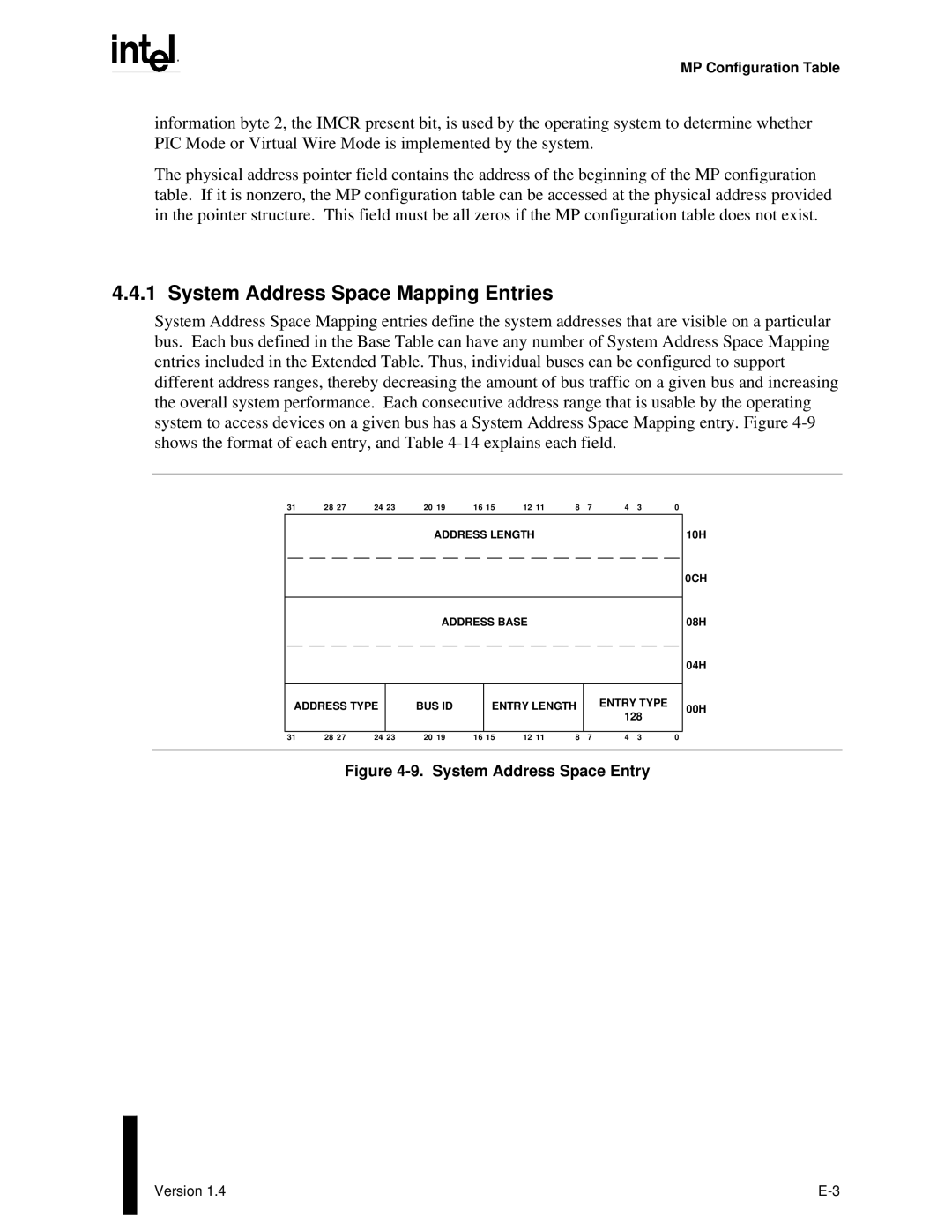

System Address Space Mapping entries define the system addresses that are visible on a particular bus. Each bus defined in the Base Table can have any number of System Address Space Mapping entries included in the Extended Table. Thus, individual buses can be configured to support different address ranges, thereby decreasing the amount of bus traffic on a given bus and increasing the overall system performance. Each consecutive address range that is usable by the operating system to access devices on a given bus has a System Address Space Mapping entry. Figure

31 | 28 27 | 24 23 | 20 19 | 16 15 | 12 11 | 8 | 7 | 4 | 3 | 0 |

ADDRESS LENGTH

ADDRESS BASE

ADDRESS TYPE | BUS ID | ENTRY LENGTH | ENTRY TYPE |

|

|

| 128 |

|

|

|

|

10H

0CH

08H

04H

00H

31 | 28 27 | 24 23 | 20 19 | 16 15 | 12 11 | 8 | 7 | 4 | 3 | 0 |

|

|

|

|

|

|

|

|

|

|

|

Figure 4-9. System Address Space Entry

Version 1.4 |