MultiProcessor Specification

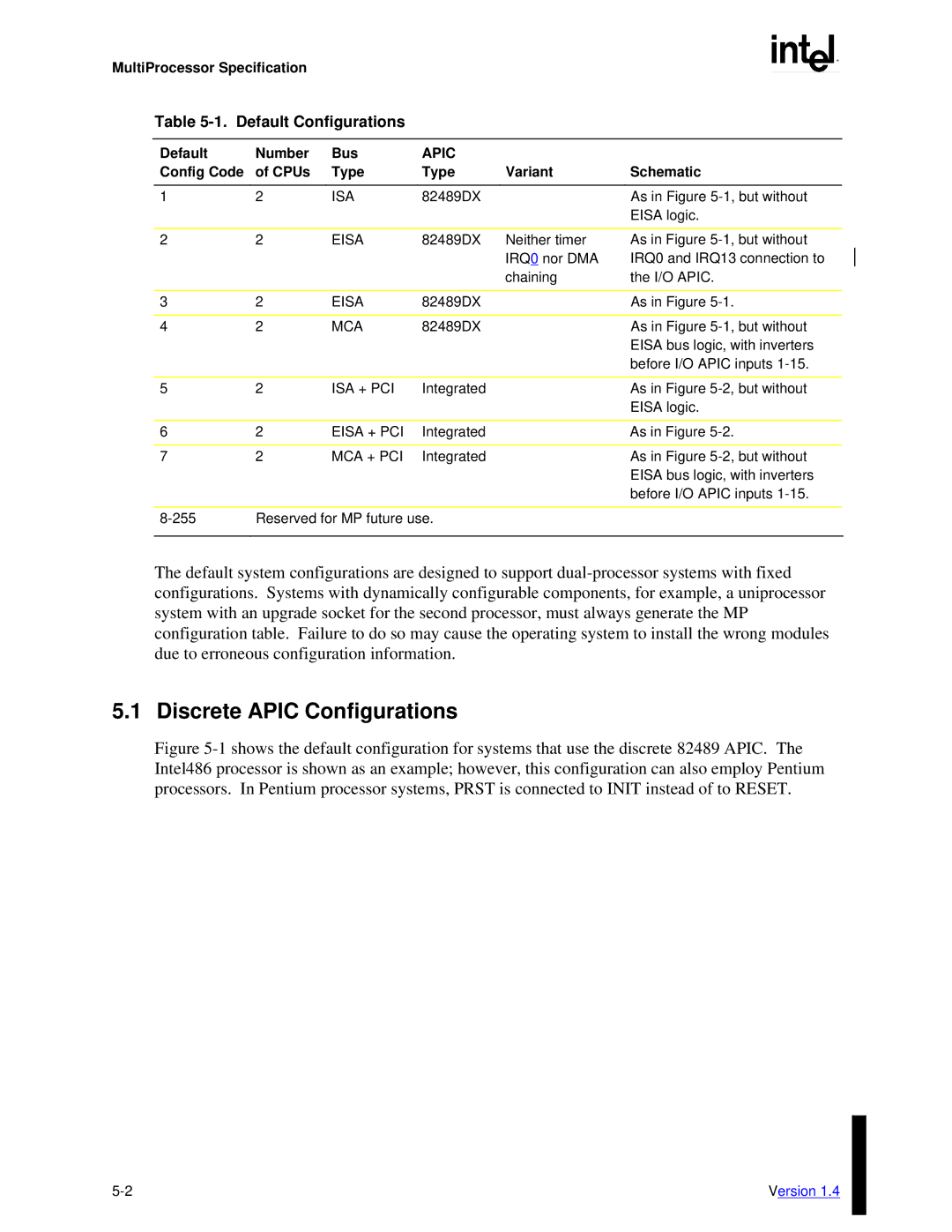

Table 5-1. Default Configurations

Default | Number | Bus | APIC |

|

|

Config Code | of CPUs | Type | Type | Variant | Schematic |

|

|

|

|

|

|

1 | 2 | ISA | 82489DX |

| As in Figure |

|

|

|

|

| EISA logic. |

|

|

|

|

|

|

2 | 2 | EISA | 82489DX | Neither timer | As in Figure |

|

|

|

| IRQ0 nor DMA | IRQ0 and IRQ13 connection to |

|

|

|

| chaining | the I/O APIC. |

|

|

|

|

|

|

3 | 2 | EISA | 82489DX |

| As in Figure |

|

|

|

|

|

|

4 | 2 | MCA | 82489DX |

| As in Figure |

|

|

|

|

| EISA bus logic, with inverters |

|

|

|

|

| before I/O APIC inputs |

|

|

|

|

|

|

5 | 2 | ISA + PCI | Integrated |

| As in Figure |

|

|

|

|

| EISA logic. |

|

|

|

|

|

|

6 | 2 | EISA + PCI | Integrated |

| As in Figure |

|

|

|

|

|

|

7 | 2 | MCA + PCI | Integrated |

| As in Figure |

|

|

|

|

| EISA bus logic, with inverters |

|

|

|

|

| before I/O APIC inputs |

|

|

|

| ||

Reserved for MP future use. |

|

| |||

|

|

|

|

|

|

The default system configurations are designed to support

5.1 Discrete APIC Configurations

Figure 5-1 shows the default configuration for systems that use the discrete 82489 APIC. The Intel486 processor is shown as an example; however, this configuration can also employ Pentium processors. In Pentium processor systems, PRST is connected to INIT instead of to RESET.

Version 1.4 |