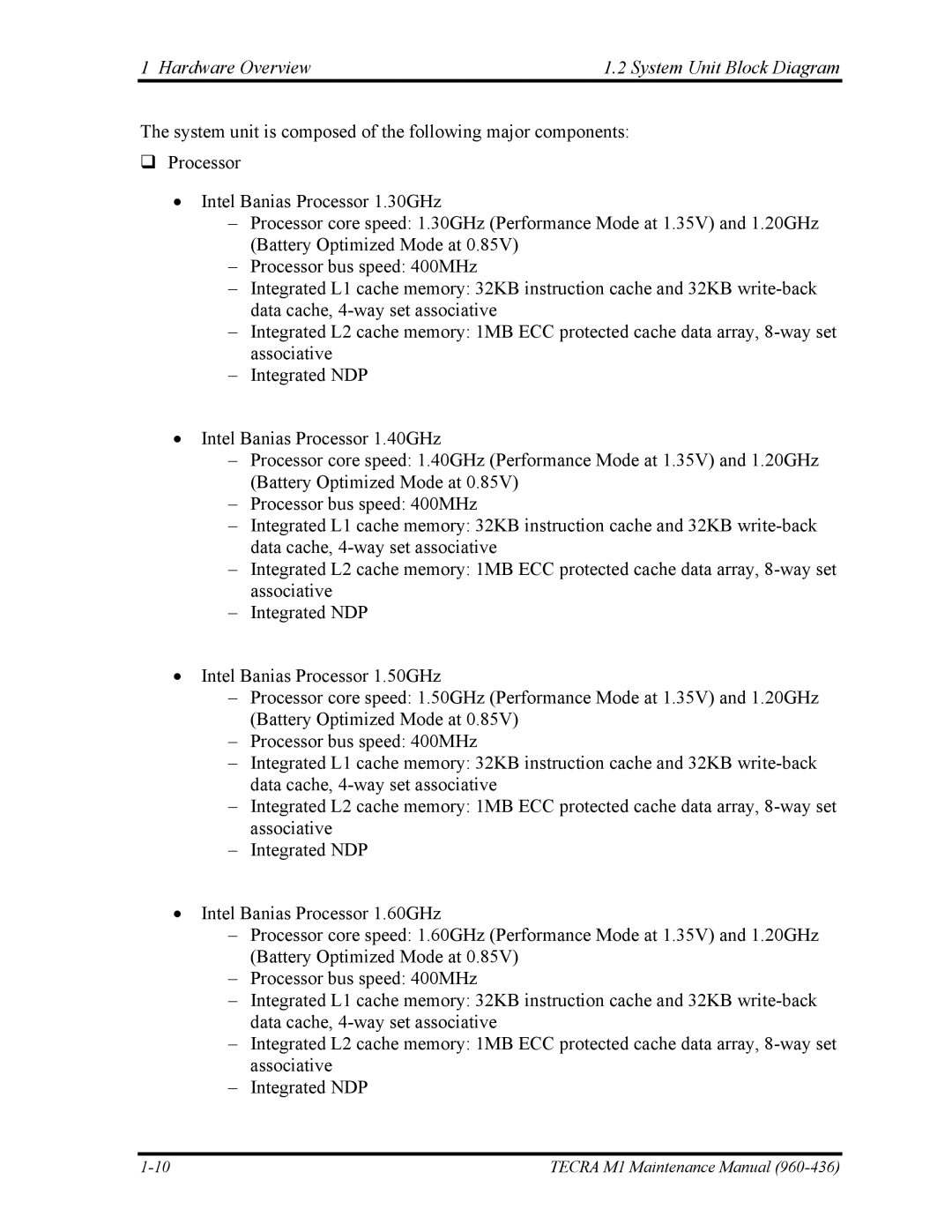

1 Hardware Overview | 1.2 System Unit Block Diagram |

The system unit is composed of the following major components:

Processor

•Intel Banias Processor 1.30GHz

–Processor core speed: 1.30GHz (Performance Mode at 1.35V) and 1.20GHz (Battery Optimized Mode at 0.85V)

–Processor bus speed: 400MHz

–Integrated L1 cache memory: 32KB instruction cache and 32KB

–Integrated L2 cache memory: 1MB ECC protected cache data array,

–Integrated NDP

•Intel Banias Processor 1.40GHz

–Processor core speed: 1.40GHz (Performance Mode at 1.35V) and 1.20GHz (Battery Optimized Mode at 0.85V)

–Processor bus speed: 400MHz

–Integrated L1 cache memory: 32KB instruction cache and 32KB

–Integrated L2 cache memory: 1MB ECC protected cache data array,

–Integrated NDP

•Intel Banias Processor 1.50GHz

–Processor core speed: 1.50GHz (Performance Mode at 1.35V) and 1.20GHz (Battery Optimized Mode at 0.85V)

–Processor bus speed: 400MHz

–Integrated L1 cache memory: 32KB instruction cache and 32KB

–Integrated L2 cache memory: 1MB ECC protected cache data array,

–Integrated NDP

•Intel Banias Processor 1.60GHz

–Processor core speed: 1.60GHz (Performance Mode at 1.35V) and 1.20GHz (Battery Optimized Mode at 0.85V)

–Processor bus speed: 400MHz

–Integrated L1 cache memory: 32KB instruction cache and 32KB

–Integrated L2 cache memory: 1MB ECC protected cache data array,

–Integrated NDP

TECRA M1 Maintenance Manual |