System Overview

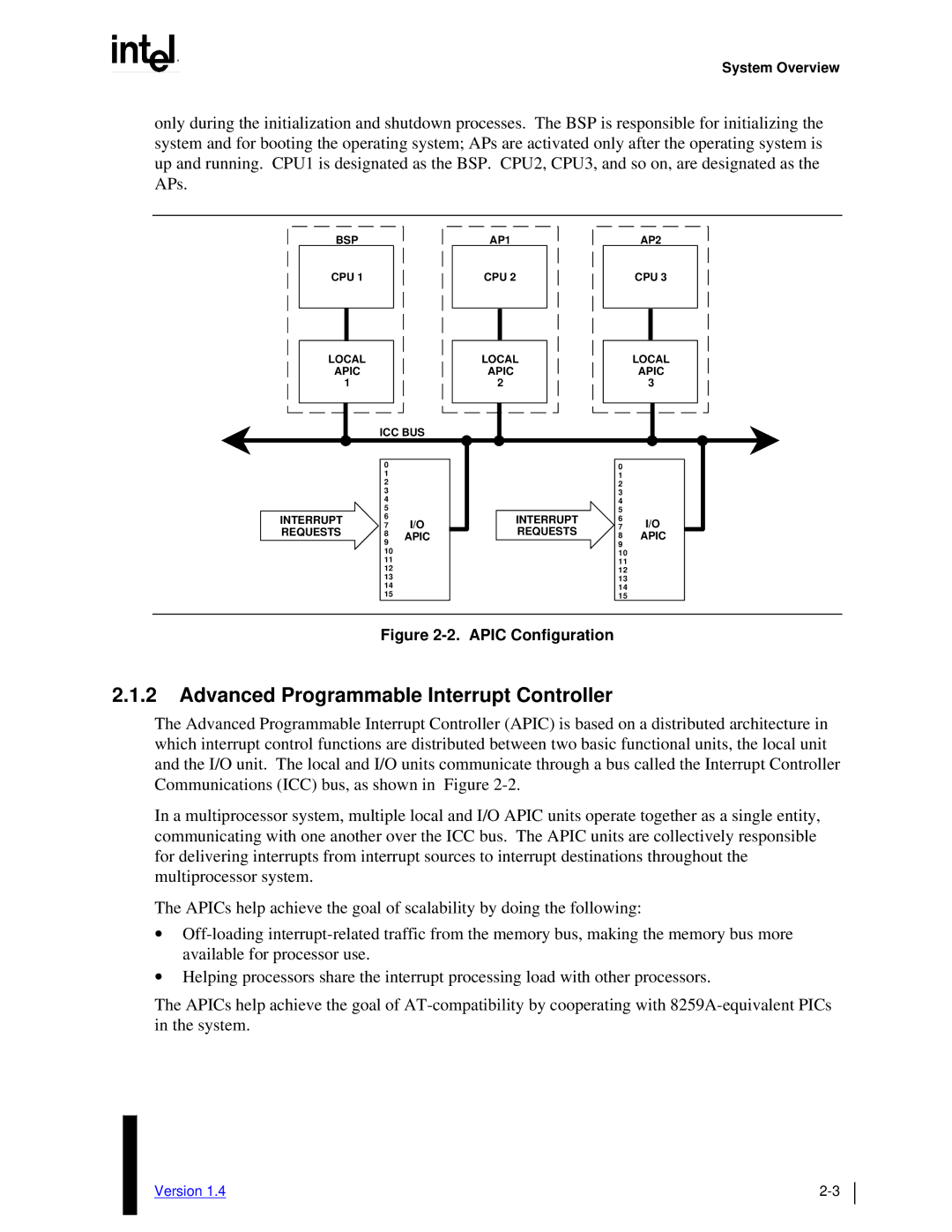

only during the initialization and shutdown processes. The BSP is responsible for initializing the system and for booting the operating system; APs are activated only after the operating system is up and running. CPU1 is designated as the BSP. CPU2, CPU3, and so on, are designated as the APs.

BSP

CPU 1

LOCAL

APIC

1

AP1

CPU 2

LOCAL

APIC

2

AP2

CPU 3

LOCAL

APIC

3

ICC BUS

| 0 |

|

| 0 |

| |

| 1 |

|

| 1 |

| |

| 2 |

|

| 2 |

| |

| 3 |

|

| 3 |

| |

| 4 |

|

| 4 |

| |

| 5 |

|

| 5 |

| |

INTERRUPT | 6 | I/O | INTERRUPT | 6 | I/O | |

7 | ||||||

REQUESTS | REQUESTS | 7 | ||||

8 | APIC | 8 | APIC | |||

| 9 |

| ||||

|

|

| 9 |

| ||

| 10 |

|

| 10 |

| |

| 11 |

|

| 11 |

| |

| 12 |

|

| 12 |

| |

| 13 |

|

| 13 |

| |

| 14 |

|

| 14 |

| |

| 15 |

|

| 15 |

|

Figure 2-2. APIC Configuration

2.1.2Advanced Programmable Interrupt Controller

The Advanced Programmable Interrupt Controller (APIC) is based on a distributed architecture in which interrupt control functions are distributed between two basic functional units, the local unit and the I/O unit. The local and I/O units communicate through a bus called the Interrupt Controller Communications (ICC) bus, as shown in Figure

In a multiprocessor system, multiple local and I/O APIC units operate together as a single entity, communicating with one another over the ICC bus. The APIC units are collectively responsible for delivering interrupts from interrupt sources to interrupt destinations throughout the multiprocessor system.

The APICs help achieve the goal of scalability by doing the following:

∙

∙Helping processors share the interrupt processing load with other processors.

The APICs help achieve the goal of

Version 1.4 |