TMS320C25

SPRS010B Ð MAY 1987 Ð REVISED NOVEMBER 1990

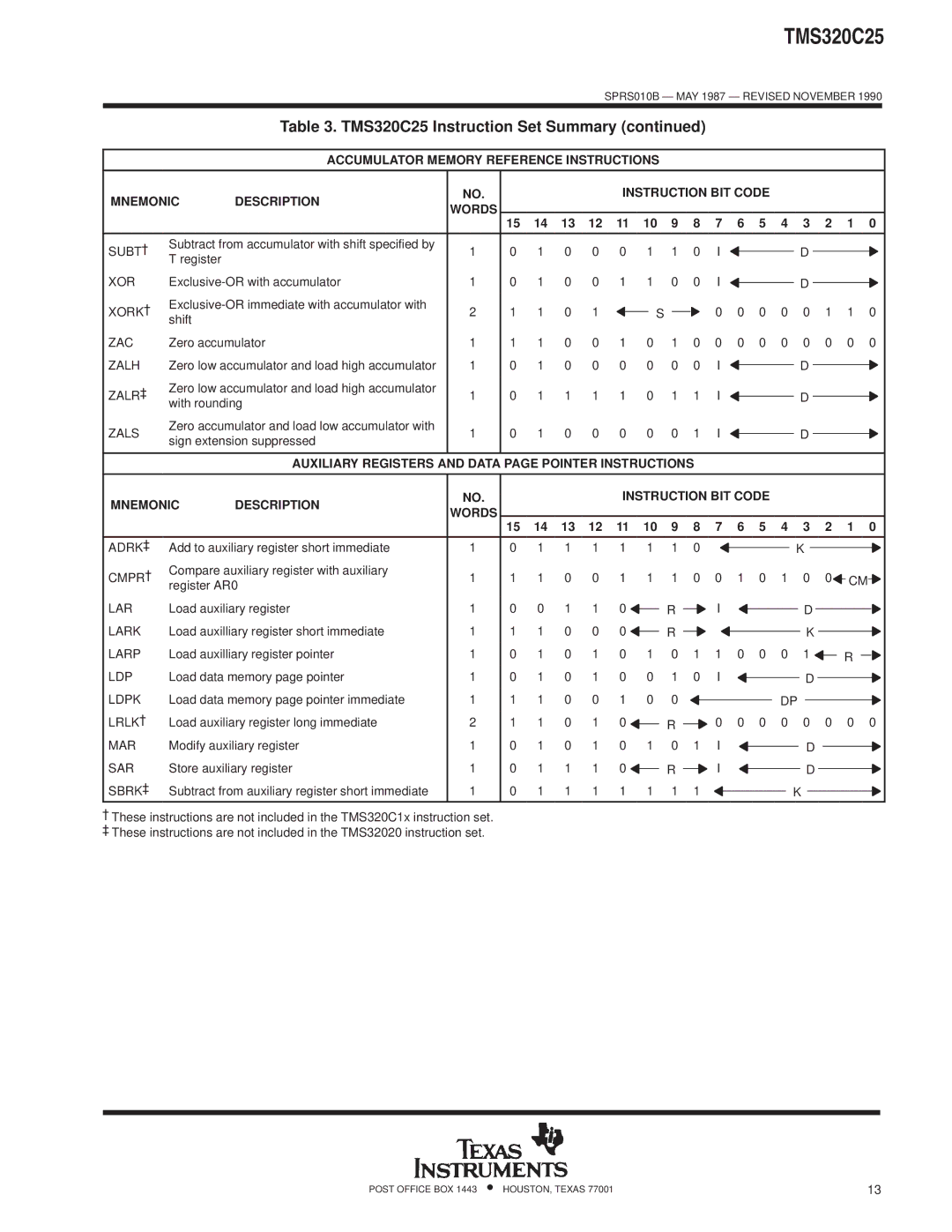

Table 3. TMS320C25 Instruction Set Summary (continued)

ACCUMULATOR MEMORY REFERENCE INSTRUCTIONS

MNEMONIC | DESCRIPTION | NO. |

|

|

|

| INSTRUCTION BIT CODE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

WORDS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| 15 | 14 | 13 | 12 | 11 | 10 |

| 9 | 8 | 7 |

| 6 | 5 | 4 | 3 |

|

|

|

|

| 2 | 1 |

| 0 | ||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

SUBT² | Subtract from accumulator with shift specified by | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| 1 | 0 |

|

| I |

|

|

|

|

|

|

| D |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

T register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

XOR | 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| 0 | 0 |

|

| I |

|

|

|

|

|

|

| D |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||||

XORK² | 2 | 1 | 1 | 0 | 1 |

|

|

|

|

|

|

|

|

|

| 0 |

| 0 | 0 | 0 | 0 |

|

|

|

|

| 1 | 1 |

| 0 | ||||||||||||||||

|

|

| S |

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||

shift |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

ZAC | Zero accumulator | 1 | 1 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 |

| 0 | 0 | 0 | 0 |

|

|

|

|

| 0 | 0 |

| 0 | ||||||||||||||||||||

ZALH | Zero low accumulator and load high accumulator | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 0 |

|

| I |

|

|

|

|

|

|

| D |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||||

ZALR³ | Zero low accumulator and load high accumulator | 1 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 1 |

|

| I |

|

|

|

|

|

|

| D |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

with rounding |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

ZALS | Zero accumulator and load low accumulator with | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 |

|

| I |

|

|

|

|

|

|

| D |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

sign extension suppressed |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

| AUXILIARY REGISTERS AND DATA PAGE POINTER INSTRUCTIONS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

MNEMONIC | DESCRIPTION | NO. |

|

|

|

| INSTRUCTION BIT CODE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

WORDS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| 15 | 14 | 13 | 12 | 11 | 10 |

| 9 | 8 | 7 |

| 6 | 5 | 4 | 3 |

|

|

|

|

| 2 | 1 |

| 0 | ||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

ADRK³ | Add to auxiliary register short immediate | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 |

|

|

|

|

|

|

|

|

|

| K |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

CMPR² | Compare auxiliary register with auxiliary | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

|

|

|

|

| 0 |

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

| CM |

|

|

|

| ||||||||||||||||||||||||||||||||||

register AR0 |

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||||||||||

LAR | Load auxiliary register | 1 | 0 | 0 | 1 | 1 | 0 |

|

|

|

|

|

|

|

|

|

| I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

| R |

|

|

|

|

|

|

|

|

|

| D |

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||

LARK | Load auxilliary register short immediate | 1 | 1 | 1 | 0 | 0 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

| R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| K |

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

LARP | Load auxilliary register pointer | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 0 | 1 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

| R |

|

|

|

|

| ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

| ||||||||||||||||||||||||||||||||||||||||

LDP | Load data memory page pointer | 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 |

|

| I |

|

|

|

|

|

|

|

| D |

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||

LDPK | Load data memory page pointer immediate | 1 | 1 | 1 | 0 | 0 | 1 | 0 |

| 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

| DP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||

LRLK² |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

Load auxiliary register long immediate | 2 | 1 | 1 | 0 | 1 | 0 |

|

|

|

|

|

|

|

| 0 |

| 0 | 0 | 0 | 0 |

|

|

|

|

| 0 | 0 |

| 0 | |||||||||||||||||

|

|

| R |

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||||||||

MAR | Modify auxiliary register | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 |

|

| I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

| D |

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||||||||

SAR | Store auxiliary register | 1 | 0 | 1 | 1 | 1 | 0 |

|

|

|

|

|

|

|

|

| I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

|

|

| R |

|

|

|

|

|

|

|

|

|

|

|

| D |

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||||||

SBRK³ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

Subtract from auxiliary register short immediate | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 |

|

|

|

|

|

|

|

|

| K |

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||||||||

²These instructions are not included in the TMS320C1x instruction set. ³ These instructions are not included in the TMS32020 instruction set.

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001 | 13 |