Contents

TMS320 SECOND-GENERATION Digital Signal Processors

Description

Signals Definition

PGA and PLCC/CER-QUAD PIN Assignments

Function PIN

Introduction

Key Features TMS32020

Bit-Reversed Indexed-Addressing Mode for

Memory Space

Wait States for Communication to Slower Off-Chip

Architecture

TMS320 Second-Generation Device Overview

Package

Type

Functional block diagram TMS320C2x

SECOND-GENERATION Devices

Timer

Scaling shifter

16 ⋅ 16-bit parallel multiplier

Memory control

TMS320 SECOND-GENERATION Devices

Memory Maps

Interrupts and subroutines

External interface

Multiprocessing

Repeat feature

Instruction set

Addressing modes

Instruction Symbols

Symbol Definition

Instruction set summary

TMS320C25 Instruction Set Summary

SUBT²

XOR

XORK²

ZAC

Apac

LPH ²

LTA

LTP ²

Data Memory Operations Mnemonic Description Words

TMS320C25 Instruction Set Summary concluded

TMS32020

TMS32020 Product Notification

Development support

TMS320 Second-Generation Software and Hardware Support

Software Tools Part Number

Hardware Tools Part Number

Specification overview

Documentation support

Recommended operating conditions

MIN NOM MAX Unit

Parameter Test Conditions MIN TYP§ MAX Unit

Clock Characteristics and Timing

Internal clock option

External clock option

Test Load Circuit

Memory and Peripheral Interface Timing

Parameter MIN TYP MAX Unit

RS, INT, BIO, and XF Timing

Hold Timing

Hold Holda

Serial Port Timing

INT Clkin / Clkx / Clkr

MP/MC IOH

TMS320C25GBA

Parameter Test Conditions MIN TYP MAX Unit

External Clock Option

Clkin

VOH Min

TdC1L-AL Low after CLKOUT1 low

Serial Port Timing

Eprom Programming

See Notes 14

VPP

IPP1

INT0 INT2 VIH

CLKIN, CLKX, Clkr

MP/MC VIL

Internal Clock Option External clock option

CLKOUT1, CLKOUT2

Fcrystal

TdC1-S From Clkout if Is present

TsuIN Setup before CLKOUT1 high

Contrast Summary of Electrical Specifications

Clock characteristics and timing

Parameter

MIN TYP MAX

Memory and peripheral interface timing

RS, INT, BIO, and XF timing

Hold timing

Serial port timing

Timing Diagrams

Clock timing

Memory read timing

BR, PS, D S

Ready

Memory write timing

CLKOUT1 CLKOUT2 Strb

One wait-state memory access timing

MSC

Reset timing

Iack

Interrupt timing TMS32020

Interrupt timing TMS320C25

Serial port receive timing

Serial port transmit timing

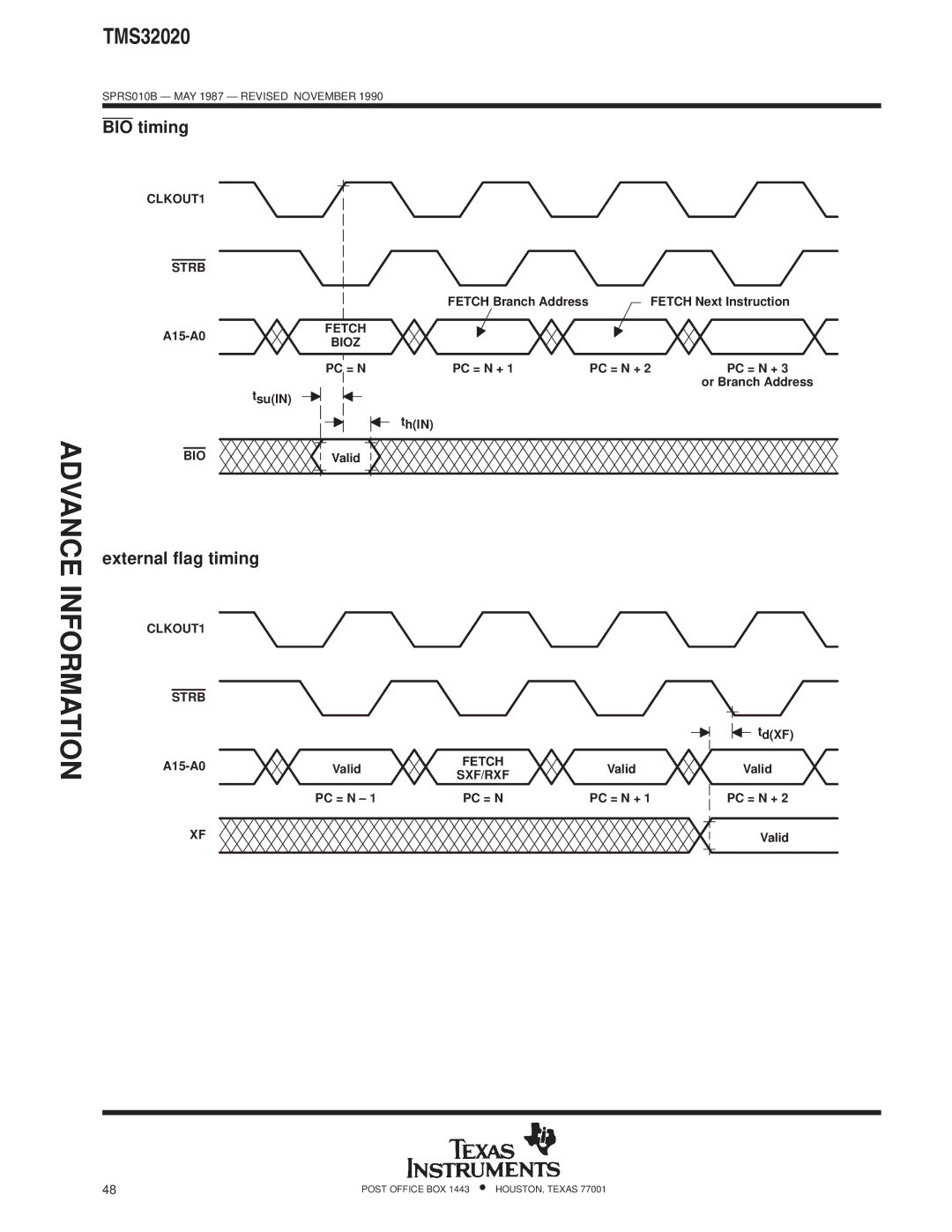

BIO timing

External flag timing

PC = N PC = N +

Hold timing part a

Hold

Holda

Execute

Hold timing part B

CLKOUT1 CLKOUT2

Holda Fetch

Fetch Execute

Or is D15-D0 TdHH-AH

Typical Supply Current Characteristics for TMS320C25

TMS320C25FNL Plcc reflow soldering precautions

Mechanical Data

Pin GB grid array ceramic package TMS32020, TMS320C25

Parameter MAX Unit

Advance

Jedec NO. Outline Terminals MIN MAX

Programming the TMS320E25 Eprom cell

Fast programming and verification

Pin Nomenclature TMS320E25

VCC

EPT

EPT VPP

TMS320E25 Programming Mode Levels

Signal

Program Read Output Name ² PIN Verify Inhibit Disable

Erasure

Fast Programming Flowchart

Program verify

Output disable

Read

ROM protection and verification

TMS320E25 Protect and Verify Eprom Mode Levels

Eprom protect

VIH VIL PGM VPP VCC

VSS Clkin EPT VPP

Eprom

Rbit

VIH VIL VPP VCC

VCC VIH VIL PGM VIH/VOH HI-Z VIL/VOL VPP EPT VSS

TMS320 SECOND-GENERATION

NIL

Packaging Information

Other Qualified Versions of TMS320C25

Important Notice