SPRS010B Ð MAY 1987 Ð REVISED NOVEMBER 1990

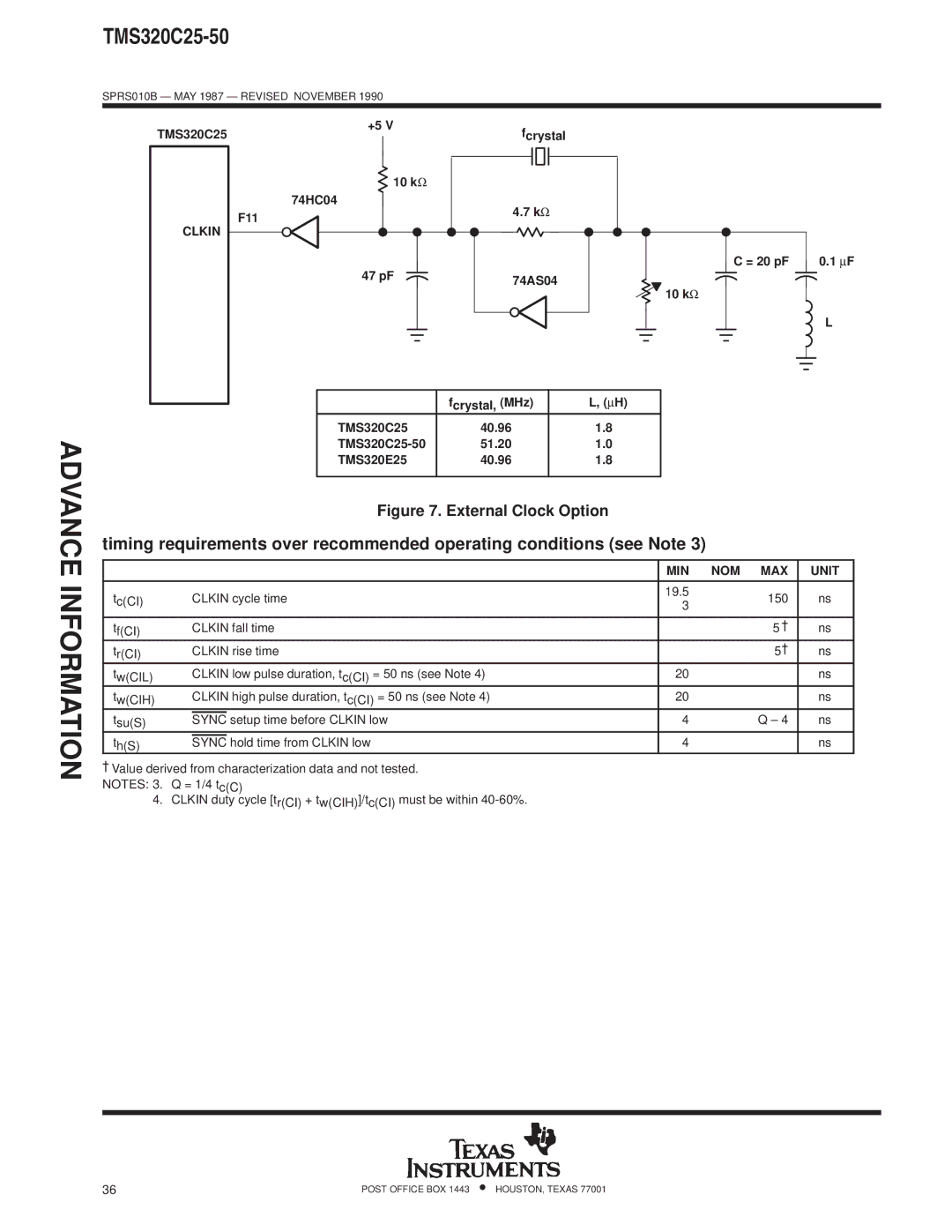

TMS320C25

CLKIN

| +5 V | fcrystal |

|

| |

| 10 kΩ |

|

| 74HC04 | 4.7 kΩ |

F11 |

| |

|

| |

| 47 pF | 74AS04 |

|

|

10 kΩ

| fcrystal, (MHz) | L, (∝H) |

TMS320C25 | 40.96 | 1.8 |

51.20 | 1.0 | |

TMS320E25 | 40.96 | 1.8 |

|

|

|

C = 20 pF

0.1∝F

L

ADVANCE INFORMATION

Figure 7. External Clock Option

timing requirements over recommended operating conditions (see Note 3)

|

|

| MIN | NOM MAX | UNIT | |

|

|

|

|

|

| |

tc(CI) | CLKIN cycle time | 19.5 | 150 | ns | ||

3 | ||||||

|

|

|

|

| ||

|

|

|

|

|

| |

t | CLKIN fall time |

| 5 ² | ns | ||

f(CI) |

|

|

|

|

| |

t | CLKIN rise time |

| 5² | ns | ||

r(CI) |

|

|

|

|

| |

tw(CIL) | CLKIN low pulse duration, tc(CI) = 50 ns (see Note 4) | 20 |

| ns | ||

tw(CIH) | CLKIN high pulse duration, tc(CI) = 50 ns (see Note 4) | 20 |

| ns | ||

tsu(S) |

| setup time before CLKIN low | 4 | Q ± 4 | ns | |

SYNC | ||||||

th(S) |

| hold time from CLKIN low | 4 |

| ns | |

SYNC |

| |||||

²Value derived from characterization data and not tested.

NOTES: 3. Q = 1/4 tc(C)

4. CLKIN duty cycle [tr(CI) + tw(CIH)]/tc(CI) must be within

36 | POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001 |