SPRS010B Ð MAY 1987 Ð REVISED NOVEMBER 1990

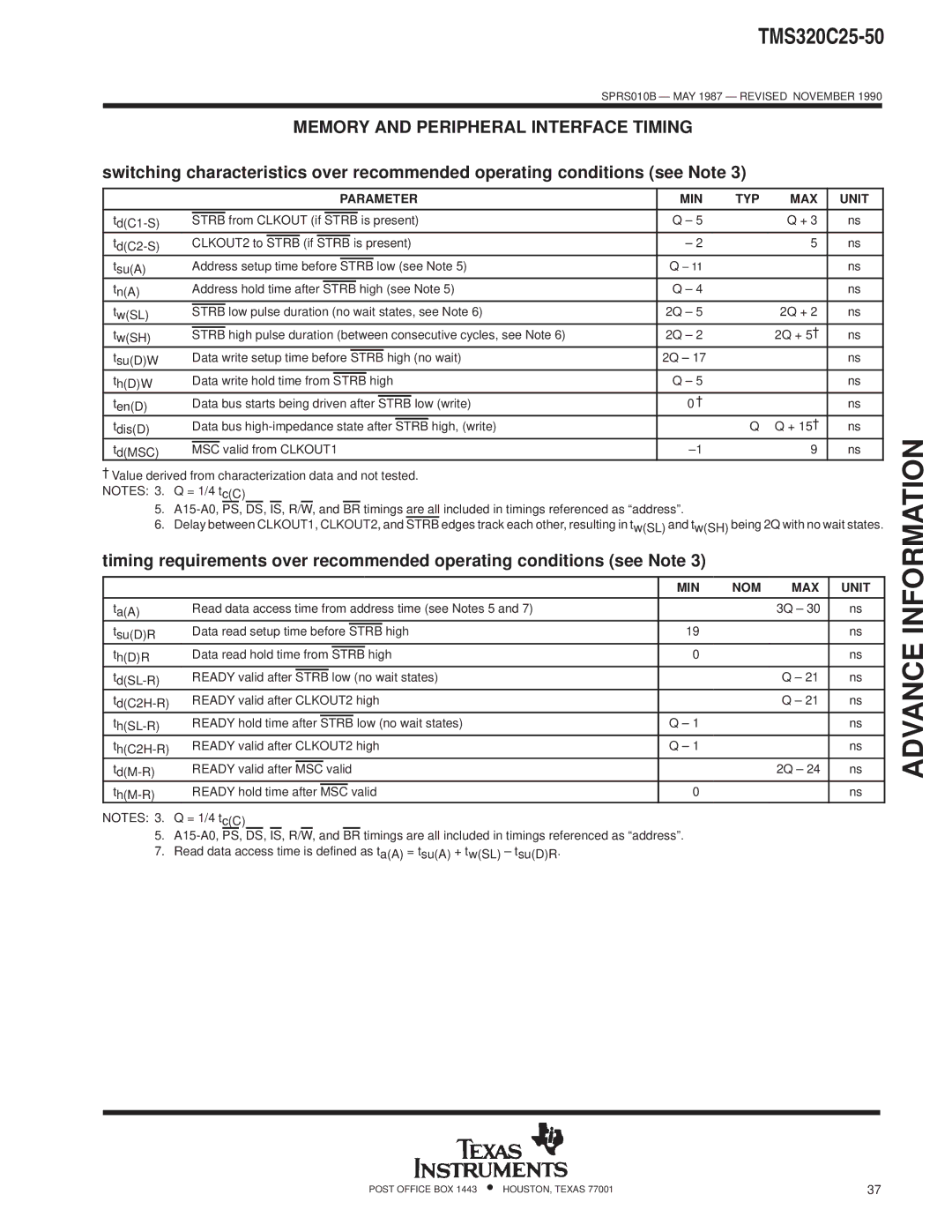

MEMORY AND PERIPHERAL INTERFACE TIMING

switching characteristics over recommended operating conditions (see Note 3)

|

|

|

|

|

|

|

|

|

| PARAMETER | MIN | TYP | MAX | UNIT | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

| from CLKOUT (if |

|

|

|

|

|

| is present) | Q ± 5 |

| Q + 3 | ns | |||||||||||

STRB |

| STRB |

| |||||||||||||||||||||||

CLKOUT2 to |

| (if |

|

|

|

|

|

| is present) | ± 2 |

| 5 | ns | |||||||||||||

STRB | STRB |

|

| |||||||||||||||||||||||

tsu(A) | Address setup time before |

|

|

|

|

|

| low (see Note 5) | Q ± 11 |

|

| ns | ||||||||||||||

STRB |

|

| ||||||||||||||||||||||||

tn(A) | Address hold time after |

|

|

|

|

|

| high (see Note 5) | Q ± 4 |

|

| ns | ||||||||||||||

STRB |

|

| ||||||||||||||||||||||||

tw(SL) |

|

|

| low pulse duration (no wait states, see Note 6) | 2Q ± 5 |

| 2Q + 2 | ns | ||||||||||||||||||

STRB |

|

| ||||||||||||||||||||||||

t |

|

|

| high pulse duration (between consecutive cycles, see Note 6) | 2Q ± 2 |

| 2Q + 5² | ns | ||||||||||||||||||

STRB |

| |||||||||||||||||||||||||

w(SH) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tsu(D)W | Data write setup time before |

|

|

|

|

|

| high (no wait) | 2Q ± 17 |

|

| ns | ||||||||||||||

STRB |

|

| ||||||||||||||||||||||||

th(D)W | Data write hold time from |

|

|

|

|

|

| high | Q ± 5 |

|

| ns | ||||||||||||||

STRB |

|

| ||||||||||||||||||||||||

t | Data bus starts being driven after |

|

|

| low (write) | 0 ² |

|

| ns | |||||||||||||||||

STRB |

|

| ||||||||||||||||||||||||

en(D) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t | Data bus |

|

| high, (write) |

| Q | Q + 15² | ns | ||||||||||||||||||

STRB |

| |||||||||||||||||||||||||

dis(D) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

td(MSC) |

| valid from CLKOUT1 | ±1 |

| 9 | ns | ||||||||||||||||||||

MSC |

| |||||||||||||||||||||||||

²Value derived from characterization data and not tested. NOTES: 3. Q = 1/4 tc(C)

5.

6.Delay between CLKOUT1, CLKOUT2, and STRB edges track each other, resulting in tw(SL) and tw(SH) being 2Q with no wait states.

timing requirements over recommended operating conditions (see Note 3)

|

|

|

|

|

|

|

|

|

|

|

|

|

| MIN | NOM | MAX | UNIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ta(A) | Read data access time from address time (see Notes 5 and 7) |

|

| 3Q ± 30 | ns | ||||||||||||

tsu(D)R | Data read setup time before |

|

|

| high | 19 |

|

| ns | ||||||||

STRB |

|

| |||||||||||||||

th(D)R | Data read hold time from |

|

|

|

| high | 0 |

|

| ns | |||||||

STRB |

|

| |||||||||||||||

READY valid after |

|

|

|

| low (no wait states) |

|

| Q ± 21 | ns | ||||||||

STRB |

|

| |||||||||||||||

READY valid after CLKOUT2 high |

|

| Q ± 21 | ns | |||||||||||||

READY hold time after |

|

|

|

|

|

| low (no wait states) | Q ± 1 |

|

| ns | ||||||

STRB |

|

| |||||||||||||||

READY valid after CLKOUT2 high | Q ± 1 |

|

| ns | |||||||||||||

READY valid after |

|

|

|

| valid |

|

| 2Q ± 24 | ns | ||||||||

MSC |

|

| |||||||||||||||

READY hold time after |

|

|

|

|

| valid | 0 |

|

| ns | |||||||

MSC |

|

| |||||||||||||||

NOTES: 3. Q = 1/4 tc(C)

5.

7. Read data access time is defined as ta(A) = tsu(A) + tw(SL) ± tsu(D)R.

ADVANCE INFORMATION

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001 | 37 |