|

|

|

|

|

| www.ti.com |

|

|

|

| |||

|

| Figure |

|

| ||

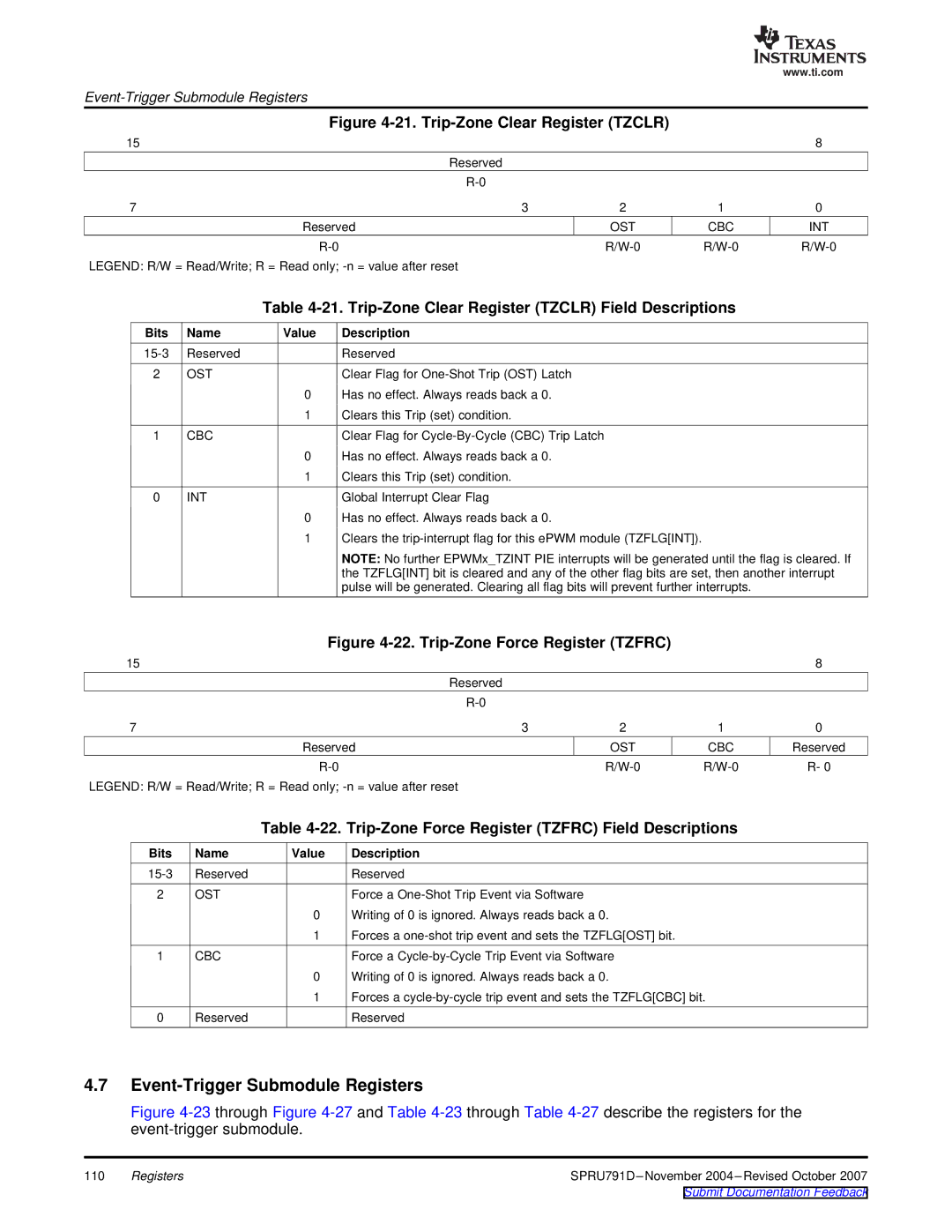

15 |

|

|

|

|

| 8 |

|

|

| Reserved |

|

|

|

|

|

|

|

|

| |

7 |

|

| 3 | 2 | 1 | 0 |

|

| Reserved | OST | CBC | INT | |

|

|

| ||||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

| |||

|

| Table |

| |||

Bits | Name | Value | Description |

|

|

|

Reserved |

| Reserved |

|

|

| |

2 | OST |

| Clear Flag for |

|

|

|

|

| 0 | Has no effect. Always reads back a 0. |

|

|

|

|

| 1 | Clears this Trip (set) condition. |

|

|

|

1 | CBC |

| Clear Flag for |

|

|

|

|

| 0 | Has no effect. Always reads back a 0. |

|

|

|

|

| 1 | Clears this Trip (set) condition. |

|

|

|

0 | INT |

| Global Interrupt Clear Flag |

|

|

|

|

| 0 | Has no effect. Always reads back a 0. |

|

|

|

|

| 1 | Clears the |

|

| |

|

|

| NOTE: No further EPWMx_TZINT PIE interrupts will be generated until the flag is cleared. If | |||

|

|

| the TZFLG[INT] bit is cleared and any of the other flag bits are set, then another interrupt | |||

|

|

| pulse will be generated. Clearing all flag bits will prevent further interrupts. |

| ||

|

| Figure |

|

| ||

15 |

|

|

|

|

| 8 |

|

|

| Reserved |

|

|

|

|

|

|

|

|

| |

7 |

|

| 3 | 2 | 1 | 0 |

|

| Reserved | OST | CBC | Reserved | |

|

|

| R- 0 | |||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

| |||

|

| Table |

| |||

Bits | Name | Value | Description |

|

|

|

Reserved |

| Reserved |

|

|

| |

2 | OST |

| Force a |

|

|

|

|

| 0 | Writing of 0 is ignored. Always reads back a 0. |

|

| |

|

| 1 | Forces a |

|

| |

1 | CBC |

| Force a |

|

| |

|

| 0 | Writing of 0 is ignored. Always reads back a 0. |

|

| |

|

| 1 | Forces a |

| ||

0 | Reserved |

| Reserved |

|

|

|

4.7Event-Trigger Submodule Registers

Figure 4-23 through Figure 4-27 and Table 4-23 through Table 4-27 describe the registers for the event-trigger submodule.

110 | Registers |